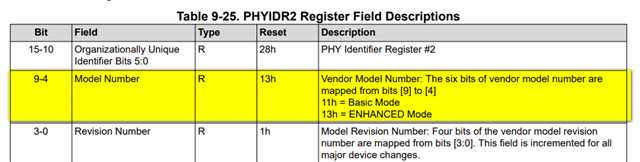

Part Number: DP83826E

Other Parts Discussed in Thread: AM6442

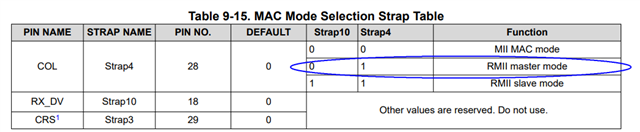

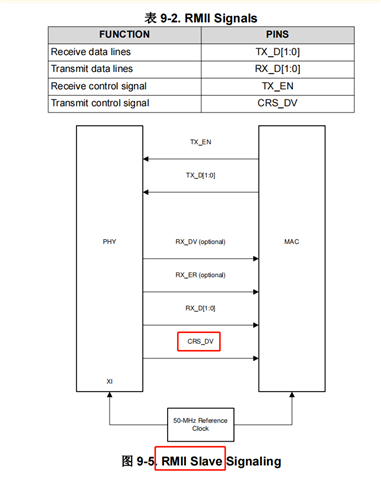

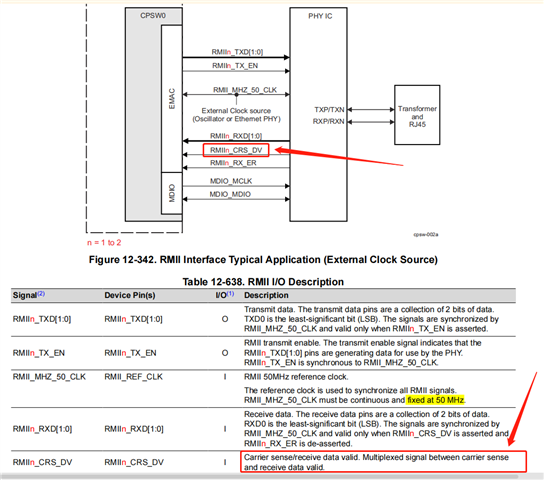

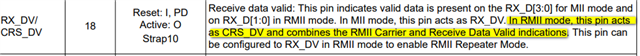

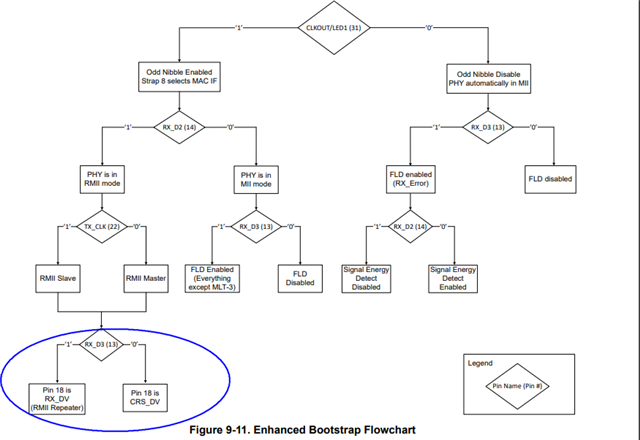

因为需要将83826E配置为RMII SLAVE MDOE, 我需要在外围电路中,将strap pin10(引脚18)和strap pin4(引脚28)上拉为高电平。 结果通过读取扩展寄存器0x468的bit 12,发现引脚18也被配置为RMII_RX_DV了。

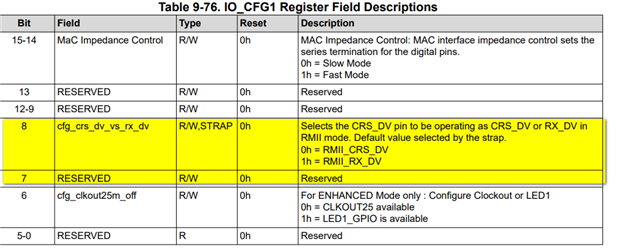

我需要将引脚18切换回RMII_CRS_DV:我通过写扩展寄存器0x302的bit8为0(写过程:先读取0x302,得到值0x0100,然后将bit8置0,即写0x0000到0x302), 然后重新读取0x302,,发现0x302值为0xcd80,与我写的值不匹配。 如果我不曾写0x302,发现读取0x302一直为0x100; 请问我该如何才能将引脚18切换回RMII_CRS_DV?