您好!

我们设备CAN接口和从设备CAN接口对接,我们设备比从设备后上电就会导致从设备CAN BUSOFF,等我们设备上电完成之后,从设备清除掉BUSOFF之后通讯都正常,而且这个现象是必现,两个设备都有120R终端电阻,请帮忙看下是什么问题导致的?

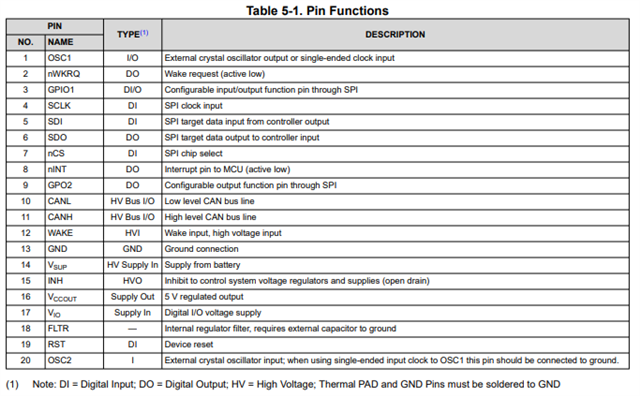

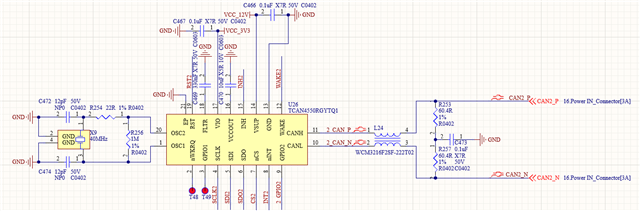

我们设备原理图如下:

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我们设备CAN接口和从设备CAN接口对接,我们设备比从设备后上电就会导致从设备CAN BUSOFF,等我们设备上电完成之后,从设备清除掉BUSOFF之后通讯都正常,而且这个现象是必现,两个设备都有120R终端电阻,请帮忙看下是什么问题导致的?

我们设备原理图如下:

TCAN4550-Q1通电进入待机模式,防止其进行CAN通信,直到设备寄存器配置为正确的值。 配置后,可将设备置于正常模式以允许CAN通信

总线关闭情况来自于太多的CAN TX或RX错误,这些错误通常是由于不兼容的设置(如额定或数据位计时)造成的。 如果设备在通电后立即进入"总线关闭"状态,则可能存在不兼容的设置。 发生这种情况时,设备将切换回待机模式,并阻止CAN通信

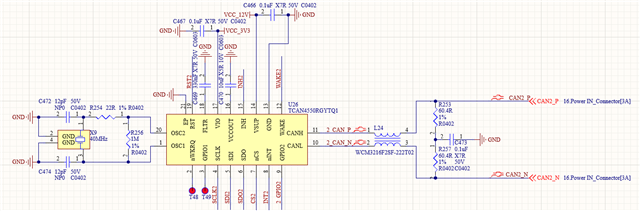

数据表显示了总线偏置在待机模式下从弱偏置到2.5V到弱偏置到GND的变化,因此这不是"异常脉冲"。

我会验证CAN设置的寄存器配置是否与总线上的其他节点匹配,以确保具有相同的标称和数据位计时配置。 我还会验证设备在完成寄存器配置之前未切换到正常模式。

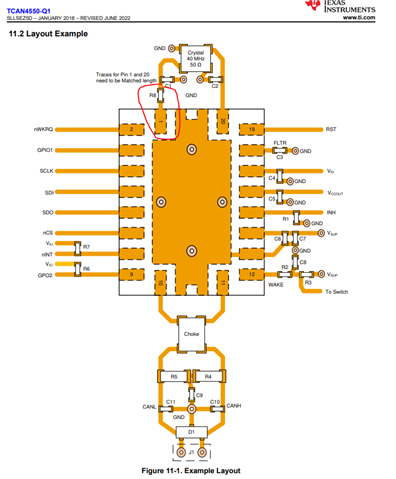

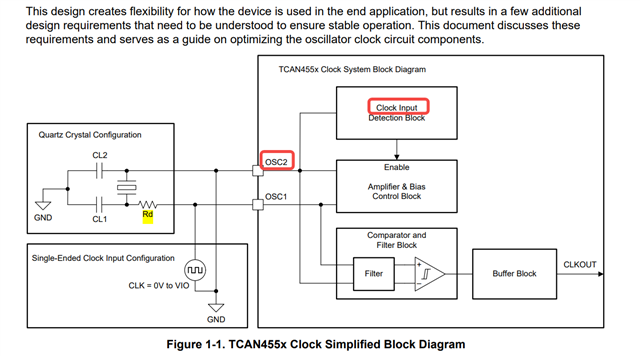

对原理图的附加注释。 我注意到R254不在晶体的正确一侧。 它通常位于OSC1引脚和晶体之间,这将允许降低来自OSC1引脚的电流,以降低晶体中的驱动电平。 这在数据表中显示,您可以在TCAN455x时钟优化和设计指南应用报告(链接)中找到更多信息

您好!

1、我会验证CAN设置的寄存器配置是否与总线上的其他节点匹配,以确保具有相同的标称和数据位计时配置。

---请问怎么验证CAN设置的寄存器配置是否与总线上的其他节点匹配?

2、对原理图的附加注释。 我注意到R254不在晶体的正确一侧。

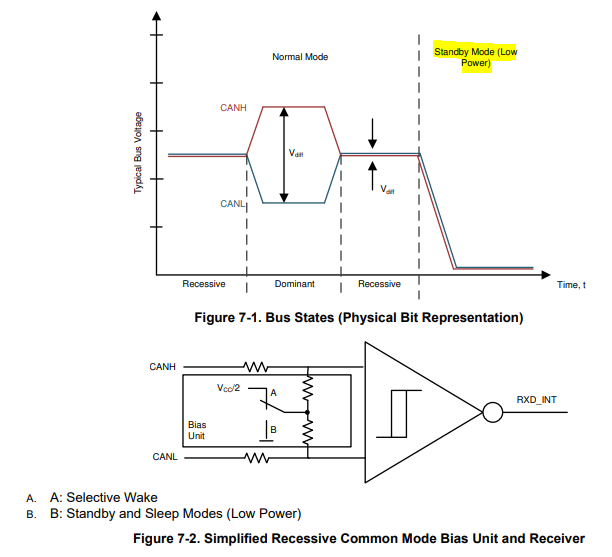

---我查看了TCAN455x时钟优化和设计指南应用报告,发现和TCAN455x的Datasheet文档有冲突地方,Datasheet里面写的OSC2是oscillator out而时钟优化和设计指南应用报告里面写的是OSC1是oscillator out?

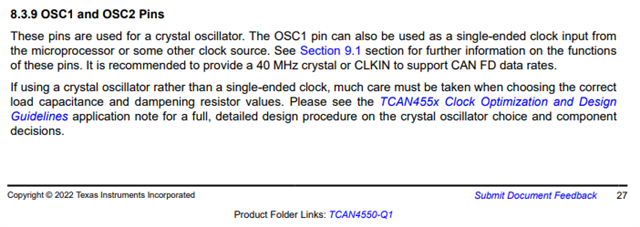

Datasheet截图如下:

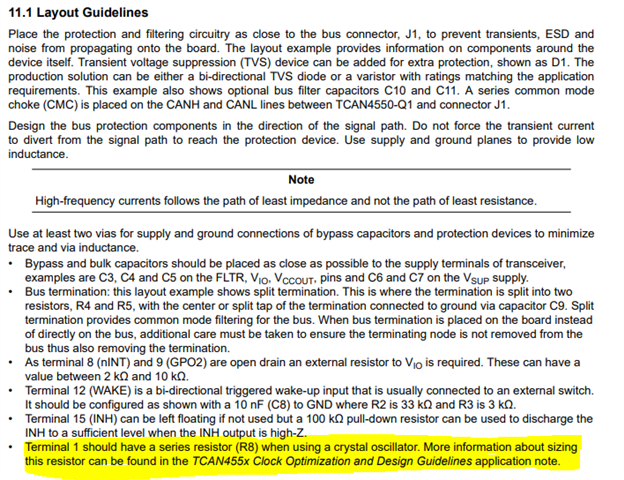

时钟优化和设计指南应用报告截图如下:

请问怎么验证CAN设置的寄存器配置是否与总线上的其他节点匹配?

您将需要确保标称和数据位计时配置与CAN总线上的其他设备匹配,我相信您在原始开机自检中称为"从设备CAN接口"。 比特计时需要匹配,如果您使用的是具有更快数据速率(启用比特率切换)的CAN FD消息,则需要确保TCAN4550-Q1的采样点%与从属设备CAN接口相同。 如果这些器件使用不同的采样点%(即一个器件为70%,另一个器件为75%),则可能存在位错误。 这是因为比特率开关发生在CAN FD消息的BRS比特内的采样点位置。 因此,如果设备之间的采样点%不同,则一台设备将先于另一台设备切换到更快的数据速率,并导致采样错误。 因此,标称比特率和数据比特率以及采样点%设置应与总线上的所有CAN节点匹配。 这是大多数应用程序的通用系统级CAN总线要求,以确保设备节点之间不存在采样错误。

我不能评论如何验证从设备上的设置可以接口,这是什么可以从MCU代码,或一些测试模块软件接口程序等查看

---我查看了TCAN455x时钟优化和设计指南应用报告,发现和TCAN455x的Datasheet文档有冲突地方,Datasheet里面写的OSC2是oscillator out而时钟优化和设计指南应用报告里面写的是OSC1是oscillator out?

您所指的不是数据表的当前版本。 这在2.5年前于2022年6月发布的数据表修订版中发生了更改。 指向时钟设计指南应用说明的链接以及需要此电阻器和正确位置的其他布局信息也添加到数据表中。

当器件在晶体模式下使用时,OSC1引脚是互阻抗放大器的"输出",OSC2引脚是振荡波形的"输入",并通过感应"低"电压或"接地OSC2引脚"检测时钟模式。 但是,当器件在单端时钟模式下使用时,互阻抗放大器将被禁用,以便OSC1引脚可以成为单端时钟信号的"输入"。