Other Parts Discussed in Thread: ALP

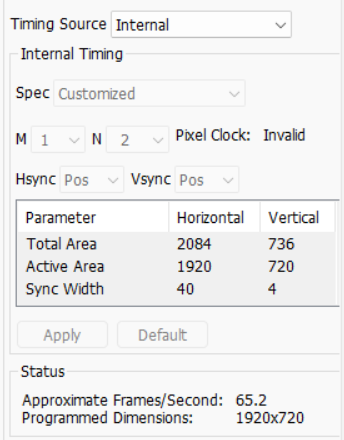

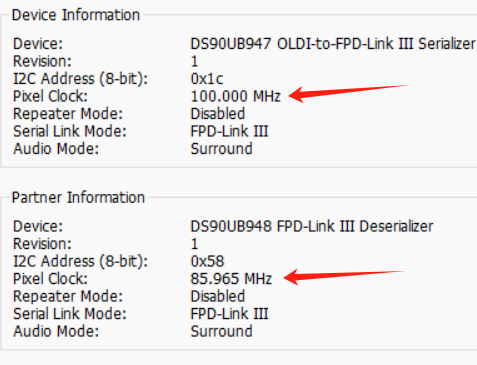

第一张图是947内部图形配置,第二张图是像素时钟。947的像素时钟计算是对的,如下:

2084*736*65.2=100,005,324,即100M。但是948的显示为85.965M。

问题1:

948的视频来源是947,那么它们的像素时钟不应该一样么?

问题2:

948的85.965M怎么计算得来的,是否有公式?

问题3:

实际测试UB948输出的LVDS时钟约46MHz,且我改变屏参为2384*1036,测量LVDS的时钟还是不变,那么948输出的LVDS时钟和什么相关?

谢谢!