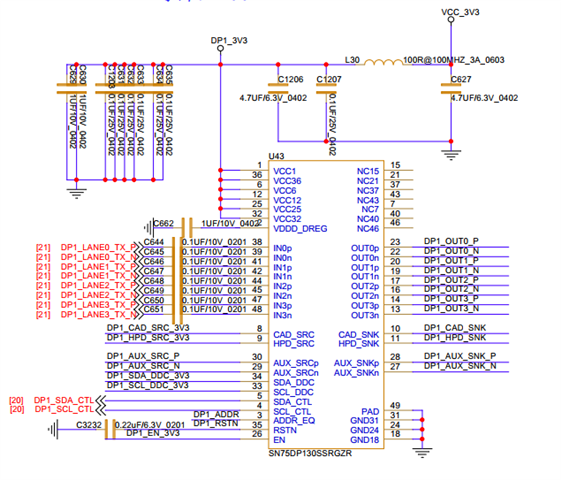

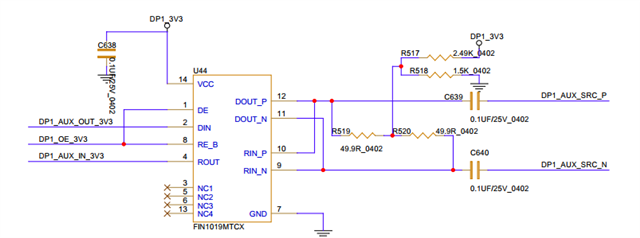

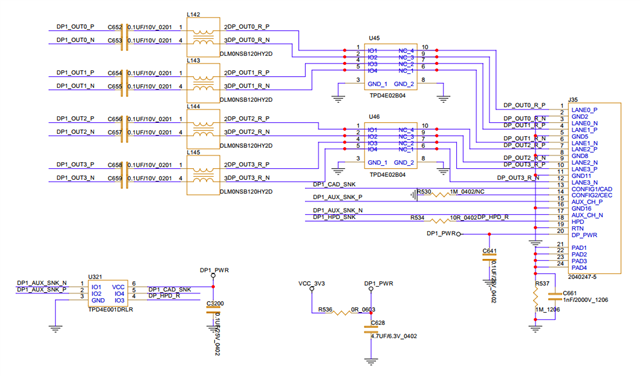

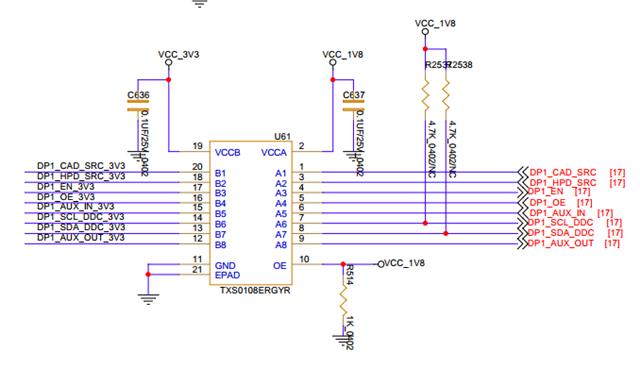

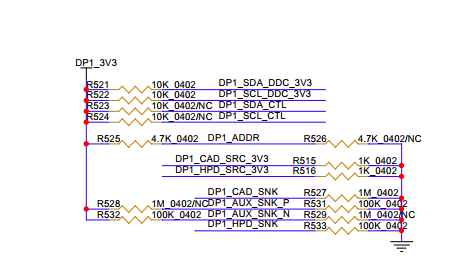

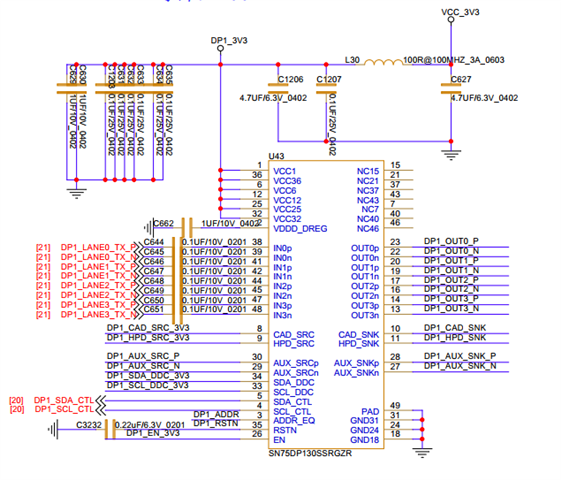

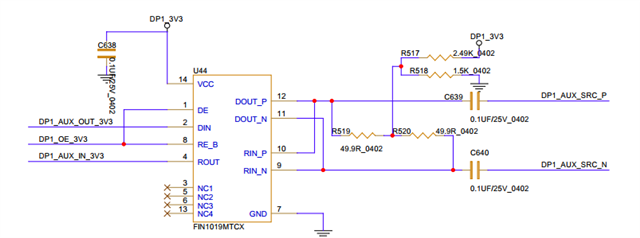

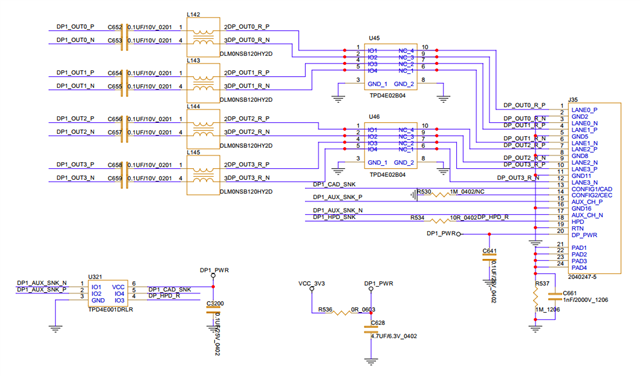

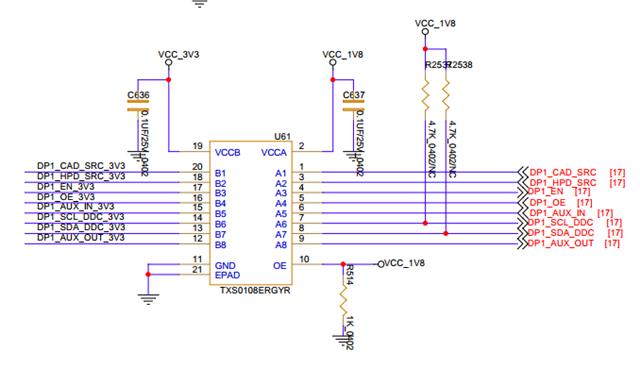

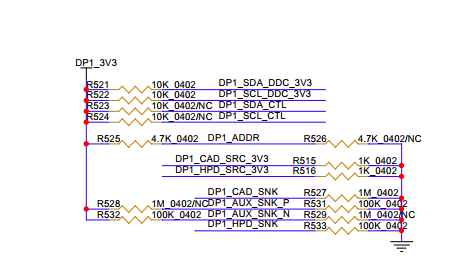

具体设计如下图:

跨页连接符连接到FPGA端。

麻烦帮忙看看硬件设计上关于DP130的设计哪里存在问题可能导致这个概率新问题。

我们测试过DP的眼图,DP输出1080p,2.7Gbps,测试结果是ok的,电源电压纹波均正常。

测试AUX通道的信号,1Mbps的速率,测试结果正常。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

具体设计如下图:

跨页连接符连接到FPGA端。

麻烦帮忙看看硬件设计上关于DP130的设计哪里存在问题可能导致这个概率新问题。

我们测试过DP的眼图,DP输出1080p,2.7Gbps,测试结果是ok的,电源电压纹波均正常。

测试AUX通道的信号,1Mbps的速率,测试结果正常。

抓取异常场景下的AUX通道信号的差异,对比测试发现是OE信号高电平的时候DP130输入端还有AUX信号,但是这个AUX信号经过DP130之后AUX信号消失了。

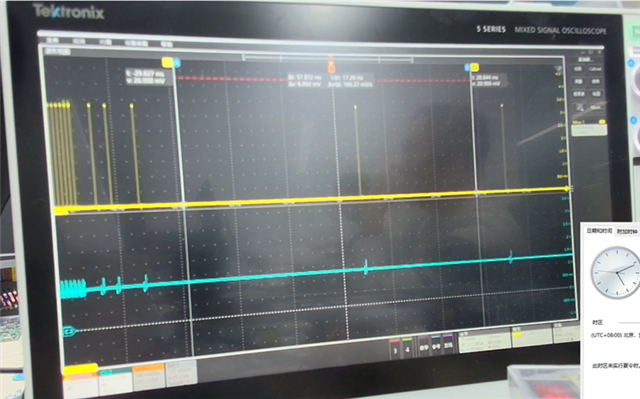

正常启动输入给DP130的AUX信号(黄色为OE信号,蓝色的AUX_P信号)

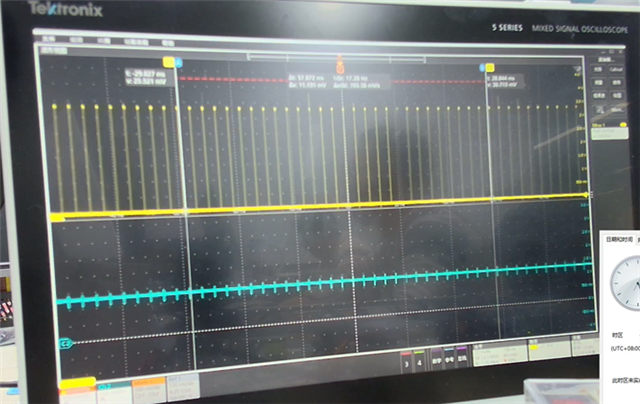

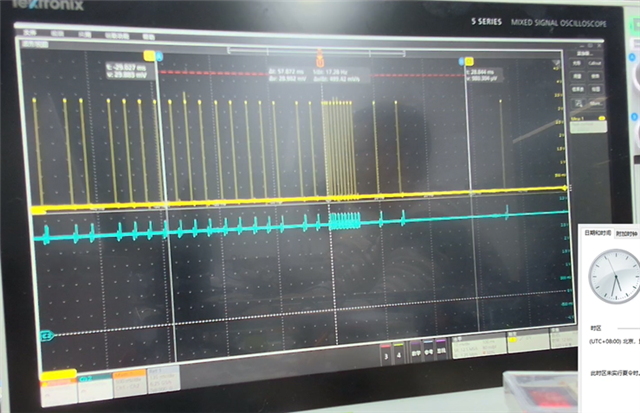

异常启动时输入给DP130的AUX信号(黄色为OE信号,蓝色的AUX_P信号)

此时FPGA一直在发送请求,但是没有反馈。

正常启动DP130输出的AUX信号(黄色为OE信号,蓝色的AUX_P信号)

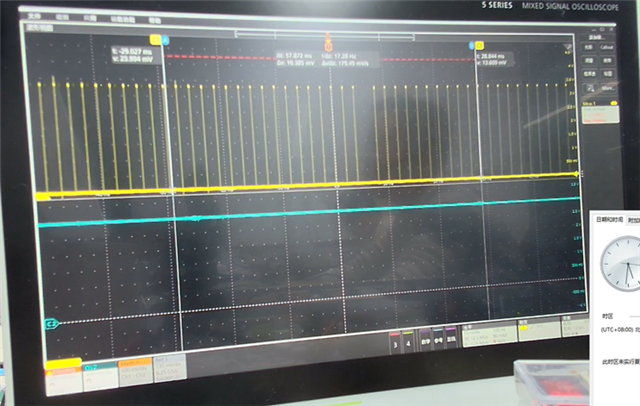

异常启动DP130输出的AUX信号(黄色为OE信号,蓝色的AUX_P信号)

对比输入给DP130的信号,此时发现DP130不再输出AUX信号了。