Part Number: DS90UB983-Q1

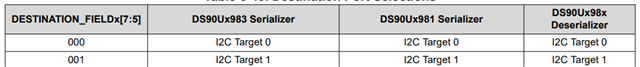

1. What is the difference between i2c1 and i2c2 of the device, and why does i2c1 read the register state differently than i2c2?

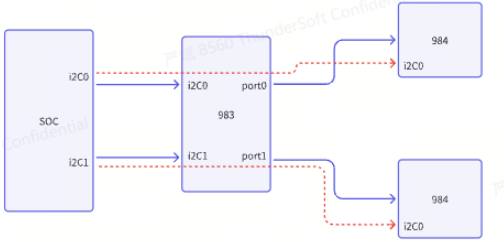

2. Now we use 983 with 984. After direct power-on, 983 cannot read the link status, nor can we read the i2c address of 984. May I ask, isn't link handshake successful by default after 983 and 984 are powered on?

thanks!