Part Number: SN65DP159

dear:

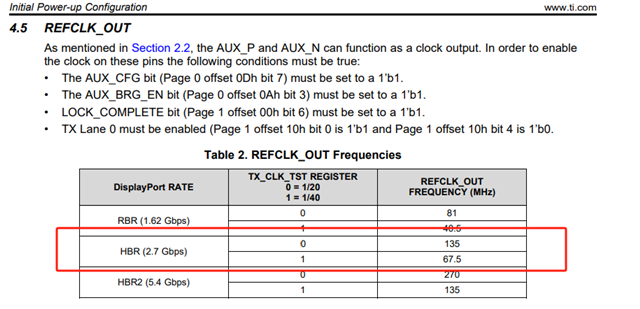

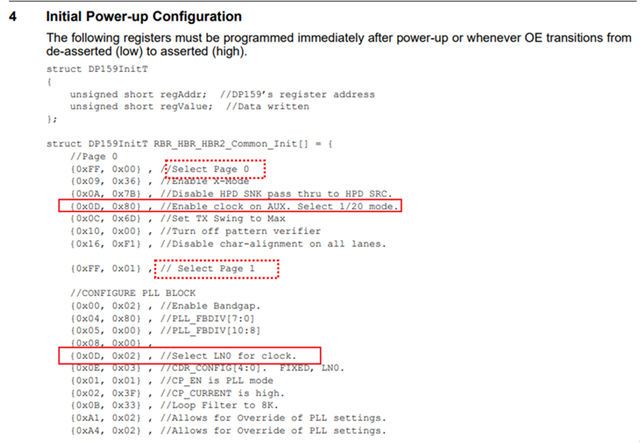

we use the SN65DP159 for FPGA EVB,we want to 135MHz output!

and setting reg. as picture( flow the datasheet) but the result of refclk_out is 280MHz

how can we set the reg. to get 135MHz ?or should we set the others reg.?

thanks