Part Number: DS250DF810

dears,

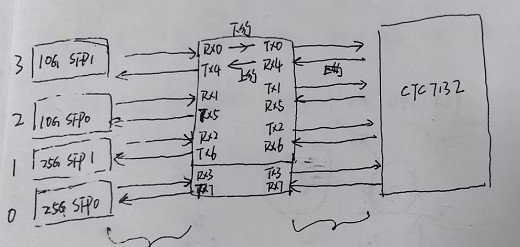

My customer used DS250DF810 between the switch chip CTC7132 and the optical module. The hardware connection block diagram is as below:

The test environment: the optical port is self-looped through the optical fiber.

The register configuration is as below:

->retimer_bpo_cfg 10

->0xffffffff (ShadowTask):1970-01-01 02:37:55<interrupt>[-1]: TEST -MAJOR set array[0]: reg = 0xfc, value = 0x1

0xffffffff (ShadowTask):1970-01-01 02:37:55<interrupt>[-1]: TEST -MAJOR set array[1]: reg = 0xff, value = 0x3

0xffffffff (ShadowTask):1970-01-01 02:37:55<interrupt>[-1]: TEST -MAJOR set array[2]: reg = 0x0, value = 0x4

0xffffffff (ShadowTask):1970-01-01 02:37:55<interrupt>[-1]: TEST -MAJOR set array[3]: reg = 0xa, value = 0xc

0xffffffff (ShadowTask):1970-01-01 02:37:55<interrupt>[-1]: TEST -MAJOR set array[4]: reg = 0x60, value = 0x27

0xffffffff (ShadowTask):1970-01-01 02:37:55<interrupt>[-1]: TEST -MAJOR set array[5]: reg = 0x61, value = 0xb1

0xffffffff (ShadowTask):1970-01-01 02:37:55<interrupt>[-1]: TEST -MAJOR set array[6]: reg = 0x62, value = 0x27

0xffffffff (ShadowTask):1970-01-01 02:37:55<interrupt>[-1]: TEST -MAJOR set array[7]: reg = 0x63, value = 0xb1

0xffffffff (ShadowTask):1970-01-01 02:37:55<interrupt>[-1]: TEST -MAJOR set array[8]: reg = 0x64, value = 0xff

0xffffffff (ShadowTask):1970-01-01 02:37:55<interrupt>[-1]: TEST -MAJOR set array[9]: reg = 0x9, value = 0x4

0xffffffff (ShadowTask):1970-01-01 02:37:55<interrupt>[-1]: TEST -MAJOR set array[10]: reg = 0x18, value = 0x10

0xffffffff (ShadowTask):1970-01-01 02:37:55<interrupt>[-1]: TEST -MAJOR set array[11]: reg = 0x31, value = 0x40

0xffffffff (ShadowTask):1970-01-01 02:37:55<interrupt>[-1]: TEST -MAJOR set array[12]: reg = 0x1e, value = 0xe3

0xffffffff (ShadowTask):1970-01-01 02:37:55<interrupt>[-1]: TEST -MAJOR set array[13]: reg = 0x3d, value = 0x9a

0xffffffff (ShadowTask):1970-01-01 02:37:55<interrupt>[-1]: TEST -MAJOR set array[14]: reg = 0x3f, value = 0x40

0xffffffff (ShadowTask):1970-01-01 02:37:55<interrupt>[-1]: TEST -MAJOR set array[15]: reg = 0x3e, value = 0x40

0xffffffff (ShadowTask):1970-01-01 02:37:55<interrupt>[-1]: TEST -MAJOR set array[16]: reg = 0x3d, value = 0x8d

0xffffffff (ShadowTask):1970-01-01 02:37:55<interrupt>[-1]: TEST -MAJOR set array[17]: reg = 0x3f, value = 0x42

0xffffffff (ShadowTask):1970-01-01 02:37:55<interrupt>[-1]: TEST -MAJOR set array[18]: reg = 0x3e, value = 0x41

0xffffffff (ShadowTask):1970-01-01 02:37:55<interrupt>[-1]: TEST -MAJOR set array[19]: reg = 0xa, value = 0x0

value = 0 = 0x0

the DF810 chip ID is read normally, the value of the 0x78 register is read as 0x20 (is it abnormal?) , the value of the 0x27 and 28 registers is read as 0x0, and the switch main chip feedback that the LINK to the optical module is not establish. the issue occurs after the CTC7132 and retimer are configured.

the customer used DS250DF810 previously and it may work normally. the issue happens after change the switch chip to CTC7132 (there is no any other change). The switch chip has been configured normally. The customer use the DS250DF810 configuration file of the previous mass-produced project. the register of DF810 is attached below:

dd_retimer_readall_debug 0

0xffffffff (ShadowTask):Global{Reg,Value}: {0xef,0xc} {0xf0,0x32} {0xf1,0x10} {0xf3,0x0} {0xfb,0x4} {0xfc,0x0} {0xfd,0x0} {0xfe,0x3} {0xff,0x0}

0xffffffff (ShadowTask):select Share Quad1, set {0xff,0x20}

0xffffffff (ShadowTask):Share Quad1{Reg,Value}: {0x0,0x0} {0x1,0x50} {0x2,0x0} {0x3,0x0} {0x4,0x9} {0x5,0x1} {0x6,0x0} {0x8,0x0} {0xa,0x0} {0xb,0x40} {0xc,0x0} {0xd,0x42} {0xe,0x3} {0xf,0x0} {0x10,0xff} {0x11,0x0} {0x12,0x91}

0xffffffff (ShadowTask):select Share Quad0, set {0xff,0x10}

0xffffffff (ShadowTask):Share Quad0{Reg,Value}: {0x0,0x0} {0x1,0x50} {0x2,0x0} {0x3,0x0} {0x4,0x9} {0x5,0x1} {0x6,0x0} {0x8,0x0} {0xa,0x0} {0xb,0x40} {0xc,0x0} {0xd,0xb4} {0xe,0x1} {0xf,0x0} {0x10,0xff} {0x11,0x0} {0x12,0x91}

0xffffffff (ShadowTask):select channel[0], set {0xfc,0x1} {0xff,0x01}

0xffffffff (ShadowTask):Channel{Reg,Value}: {0x0,0x0} {0x1,0x80} {0x2,0x1} {0x3,0x0} {0x4,0x1} {0x5,0x1} {0x6,0x1} {0x7,0x1} {0x8,0x73} {0x9,0x0} {0xa,0x0} {0xb,0x63} {0xc,0x0} {0xd,0x80} {0xe,0x93} {0xf,0x69}

0xffffffff (ShadowTask):Channel{Reg,Value}: {0x10,0x0} {0x11,0x20} {0x12,0x83} {0x13,0xb0} {0x14,0x4} {0x15,0x10} {0x16,0x7a} {0x17,0x36} {0x18,0x40} {0x19,0x20} {0x1a,0x58} {0x1b,0x3} {0x1c,0x90} {0x1d,0x0} {0x1e,0xe9} {0x1f,0xb}

0xffffffff (ShadowTask):Channel{Reg,Value}: {0x20,0x0} {0x21,0x0} {0x22,0x0} {0x23,0x40} {0x24,0x40} {0x25,0x0} {0x26,0x0} {0x27,0x0} {0x28,0x0} {0x29,0x3} {0x2a,0x5a} {0x2b,0xa} {0x2c,0xf6} {0x2d,0x30} {0x2e,0x0} {0x2f,0x54}

0xffffffff (ShadowTask):Channel{Reg,Value}: {0x30,0x0} {0x31,0x20} {0x32,0x11} {0x33,0x88} {0x34,0xbf} {0x35,0xf} {0x36,0x30} {0x37,0x5} {0x38,0x0} {0x39,0x60} {0x3a,0x0} {0x3b,0x3f} {0x3c,0x6b} {0x3d,0x1a} {0x3e,0x40} {0x3f,0x40}

0xffffffff (ShadowTask):Channel{Reg,Value}: {0x40,0x0} {0x41,0x40} {0x42,0x50} {0x43,0x80} {0x44,0x90} {0x45,0xc0} {0x46,0xd0} {0x47,0xd1} {0x48,0xd5} {0x49,0xd8} {0x4a,0xea} {0x4b,0xf7} {0x4c,0xfd} {0x4d,0xee} {0x4e,0xef} {0x4f,0xff}

0xffffffff (ShadowTask):Channel{Reg,Value}: {0x50,0x0} {0x51,0x0} {0x52,0x0} {0x53,0x0} {0x54,0x0} {0x55,0x0} {0x56,0x0} {0x57,0x0} {0x58,0x0} {0x59,0x0} {0x5a,0x0} {0x5b,0x0} {0x5c,0x0} {0x5d,0x0} {0x5e,0x0} {0x5f,0x0}

0xffffffff (ShadowTask):Channel{Reg,Value}: {0x60,0x0} {0x61,0x0} {0x62,0x0} {0x63,0x0} {0x64,0x0} {0x65,0x0} {0x66,0x0} {0x67,0x20} {0x68,0x0} {0x69,0xa} {0x6a,0x21} {0x6b,0x40} {0x6c,0x0} {0x6d,0x0} {0x6e,0x0} {0x6f,0x0}

0xffffffff (ShadowTask):Channel{Reg,Value}: {0x70,0x5} {0x71,0x23} {0x72,0x0} {0x73,0x0} {0x74,0x0} {0x75,0x0} {0x76,0x21} {0x77,0x1a} {0x78,0x20} {0x79,0x10} {0x7a,0x0} {0x7b,0x0} {0x7c,0x0} {0x7d,0x48} {0x7e,0x13} {0x7f,0x2a}

0xffffffff (ShadowTask):Channel{Reg,Value}: {0x80,0x0} {0x81,0xe5} {0x82,0x0} {0x83,0x1} {0x84,0x0} {0x85,0x0} {0x86,0x0} {0x87,0x0} {0x88,0x0} {0x89,0x0} {0x8a,0x0} {0x8b,0x0} {0x8c,0x0} {0x8d,0x0} {0x8e,0x0} {0x8f,0x0}

0xffffffff (ShadowTask):Channel{Reg,Value}: {0x90,0x0} {0x91,0x0} {0x92,0x0} {0x93,0x0} {0x94,0x0} {0x95,0x0} {0x96,0x8} {0x97,0xff} {0x98,0x0} {0x99,0x3f} {0x9a,0x3f} {0x9b,0xe0} {0x9c,0x24} {0x9d,0xa5} {0x9e,0x48} {0x9f,0x0}

0xffffffff (ShadowTask):Channel{Reg,Value}: {0xa0,0x0} {0xa1,0x40} {0xa2,0x50} {0xa3,0x80} {0xa4,0x90} {0xa5,0x20} {0xa6,0x43} {0xa7,0xdf} {0xa8,0x0} {0xa9,0x0}

value = 0 = 0x0

retimer_sct_cfg 0,10

0xffffffff (ShadowTask):1970-01-01 00:08:07<interrupt>[-1]: TEST -MAJOR set array[0]: reg = 0xff, value = 0x1

0xffffffff (ShadowTask):1970-01-01 00:08:07<interrupt>[-1]: TEST -MAJOR set array[0]: reg = 0xfc, value = 0x1

0xffffffff (ShadowTask):1970-01-01 00:08:07<interrupt>[-1]: TEST -MAJOR set array[0]: reg = 0xff, value = 0x1

0xffffffff (ShadowTask):1970-01-01 00:08:07<interrupt>[-1]: TEST -MAJOR set array[1]: reg = 0xfc, value = 0x1

0xffffffff (ShadowTask):1970-01-01 00:08:07<interrupt>[-1]: TEST -MAJOR set array[2]: reg = 0x0, value = 0x4

0xffffffff (ShadowTask):1970-01-01 00:08:07<interrupt>[-1]: TEST -MAJOR set array[3]: reg = 0xa, value = 0xc

0xffffffff (ShadowTask):1970-01-01 00:08:07<interrupt>[-1]: TEST -MAJOR set array[4]: reg = 0x60, value = 0x90

0xffffffff (ShadowTask):1970-01-01 00:08:07<interrupt>[-1]: TEST -MAJOR set array[5]: reg = 0x61, value = 0xb3

0xffffffff (ShadowTask):1970-01-01 00:08:07<interrupt>[-1]: TEST -MAJOR set array[6]: reg = 0x62, value = 0x90

0xffffffff (ShadowTask):1970-01-01 00:08:07<interrupt>[-1]: TEST -MAJOR set array[7]: reg = 0x63, value = 0xb3

0xffffffff (ShadowTask):1970-01-01 00:08:07<interrupt>[-1]: TEST -MAJOR set array[8]: reg = 0x64, value = 0xff

0xffffffff (ShadowTask):1970-01-01 00:08:07<interrupt>[-1]: TEST -MAJOR set array[9]: reg = 0x9, value = 0x4

0xffffffff (ShadowTask):1970-01-01 00:08:07<interrupt>[-1]: TEST -MAJOR set array[10]: reg = 0x18, value = 0x10

0xffffffff (ShadowTask):1970-01-01 00:08:07<interrupt>[-1]: TEST -MAJOR set array[11]: reg = 0x31, value = 0x40

0xffffffff (ShadowTask):1970-01-01 00:08:07<interrupt>[-1]: TEST -MAJOR set array[12]: reg = 0x1e, value = 0xe3

0xffffffff (ShadowTask):1970-01-01 00:08:07<interrupt>[-1]: TEST -MAJOR set array[13]: reg = 0x3d, value = 0x9a

0xffffffff (ShadowTask):1970-01-01 00:08:07<interrupt>[-1]: TEST -MAJOR set array[14]: reg = 0x3d, value = 0x9a

0xffffffff (ShadowTask):1970-01-01 00:08:07<interrupt>[-1]: TEST -MAJOR set array[15]: reg = 0x3f, value = 0x40

0xffffffff (ShadowTask):1970-01-01 00:08:07<interrupt>[-1]: TEST -MAJOR set array[16]: reg = 0x3e, value = 0x40

0xffffffff (ShadowTask):1970-01-01 00:08:07<interrupt>[-1]: TEST -MAJOR set array[17]: reg = 0x3d, value = 0x8a

0xffffffff (ShadowTask):1970-01-01 00:08:08<interrupt>[-1]: TEST -MAJOR set array[18]: reg = 0x3f, value = 0x41

0xffffffff (ShadowTask):1970-01-01 00:08:08<interrupt>[-1]: TEST -MAJOR set array[19]: reg = 0x3e, value = 0x41

0xffffffff (ShadowTask):1970-01-01 00:08:08<interrupt>[-1]: TEST -MAJOR set array[20]: reg = 0xa, value = 0x0

value = 0 = 0x0

->

->

->dd_retimer_readall_debug 0

->0xffffffff (ShadowTask):Global{Reg,Value}: {0xef,0xc} {0xf0,0x32} {0xf1,0x10} {0xf3,0x0} {0xfb,0x4} {0xfc,0x1} {0xfd,0x0} {0xfe,0x3} {0xff,0x1}

0xffffffff (ShadowTask):select Share Quad1, set {0xff,0x20}

0xffffffff (ShadowTask):Share Quad1{Reg,Value}: {0x0,0x0} {0x1,0x50} {0x2,0x0} {0x3,0x0} {0x4,0x9} {0x5,0x1} {0x6,0x0} {0x8,0x0} {0xa,0x0} {0xb,0x40} {0xc,0x0} {0xd,0x42} {0xe,0x3} {0xf,0x0} {0x10,0xff} {0x11,0x0} {0x12,0x91}

0xffffffff (ShadowTask):select Share Quad0, set {0xff,0x10}

0xffffffff (ShadowTask):Share Quad0{Reg,Value}: {0x0,0x0} {0x1,0x50} {0x2,0x0} {0x3,0x0} {0x4,0x9} {0x5,0x1} {0x6,0x0} {0x8,0x0} {0xa,0x0} {0xb,0x40} {0xc,0x0} {0xd,0xb4} {0xe,0x1} {0xf,0x0} {0x10,0xff} {0x11,0x0} {0x12,0x91}

0xffffffff (ShadowTask):select channel[0], set {0xfc,0x1} {0xff,0x01}

0xffffffff (ShadowTask):Channel{Reg,Value}: {0x0,0x0} {0x1,0x80} {0x2,0x0} {0x3,0x0} {0x4,0x1} {0x5,0x1} {0x6,0x1} {0x7,0x1} {0x8,0x73} {0x9,0x4} {0xa,0x0} {0xb,0x63} {0xc,0x0} {0xd,0x80} {0xe,0x93} {0xf,0x69}

0xffffffff (ShadowTask):Channel{Reg,Value}: {0x10,0x0} {0x11,0x20} {0x12,0x83} {0x13,0xb0} {0x14,0x4} {0x15,0x10} {0x16,0x7a} {0x17,0x36} {0x18,0x10} {0x19,0x20} {0x1a,0x58} {0x1b,0x3} {0x1c,0x90} {0x1d,0x0} {0x1e,0xe3} {0x1f,0xb}

0xffffffff (ShadowTask):Channel{Reg,Value}: {0x20,0x0} {0x21,0x0} {0x22,0x0} {0x23,0x40} {0x24,0x40} {0x25,0x0} {0x26,0x0} {0x27,0x0} {0x28,0x0} {0x29,0x3} {0x2a,0x5a} {0x2b,0xa} {0x2c,0xf6} {0x2d,0x30} {0x2e,0x0} {0x2f,0x54}

0xffffffff (ShadowTask):Channel{Reg,Value}: {0x30,0x0} {0x31,0x40} {0x32,0x11} {0x33,0x88} {0x34,0xbf} {0x35,0xf} {0x36,0x30} {0x37,0x9} {0x38,0x0} {0x39,0x60} {0x3a,0x0} {0x3b,0x32} {0x3c,0xe6} {0x3d,0x8a} {0x3e,0x41} {0x3f,0x41}

0xffffffff (ShadowTask):Channel{Reg,Value}: {0x40,0x0} {0x41,0x40} {0x42,0x50} {0x43,0x80} {0x44,0x90} {0x45,0xc0} {0x46,0xd0} {0x47,0xd1} {0x48,0xd5} {0x49,0xd8} {0x4a,0xea} {0x4b,0xf7} {0x4c,0xfd} {0x4d,0xee} {0x4e,0xef} {0x4f,0xff}

0xffffffff (ShadowTask):Channel{Reg,Value}: {0x50,0x0} {0x51,0x0} {0x52,0x0} {0x53,0x0} {0x54,0x0} {0x55,0x0} {0x56,0x0} {0x57,0x0} {0x58,0x0} {0x59,0x0} {0x5a,0x0} {0x5b,0x0} {0x5c,0x0} {0x5d,0x0} {0x5e,0x0} {0x5f,0x0}

0xffffffff (ShadowTask):Channel{Reg,Value}: {0x60,0x90} {0x61,0xb3} {0x62,0x90} {0x63,0xb3} {0x64,0xff} {0x65,0x0} {0x66,0x0} {0x67,0x20} {0x68,0x0} {0x69,0xa} {0x6a,0x21} {0x6b,0x40} {0x6c,0x0} {0x6d,0x0} {0x6e,0x0} {0x6f,0x0}

0xffffffff (ShadowTask):Channel{Reg,Value}: {0x70,0x5} {0x71,0x23} {0x72,0x0} {0x73,0x0} {0x74,0x0} {0x75,0x0} {0x76,0x21} {0x77,0x1a} {0x78,0x20} {0x79,0x10} {0x7a,0x0} {0x7b,0x0} {0x7c,0x0} {0x7d,0x48} {0x7e,0x13} {0x7f,0x2a}

0xffffffff (ShadowTask):Channel{Reg,Value}: {0x80,0x0} {0x81,0xe5} {0x82,0x0} {0x83,0x1} {0x84,0x0} {0x85,0x0} {0x86,0x0} {0x87,0x0} {0x88,0x0} {0x89,0x0} {0x8a,0x0} {0x8b,0x0} {0x8c,0x0} {0x8d,0x0} {0x8e,0x0} {0x8f,0x90}

0xffffffff (ShadowTask):Channel{Reg,Value}: {0x90,0x0} {0x91,0x0} {0x92,0x0} {0x93,0x0} {0x94,0x0} {0x95,0x0} {0x96,0x8} {0x97,0xff} {0x98,0x0} {0x99,0x3f} {0x9a,0x3f} {0x9b,0xe0} {0x9c,0x24} {0x9d,0xa5} {0x9e,0x48} {0x9f,0x0}

0xffffffff (ShadowTask):Channel{Reg,Value}: {0xa0,0x0} {0xa1,0x40} {0xa2,0x50} {0xa3,0x80} {0xa4,0x90} {0xa5,0x20} {0xa6,0x43} {0xa7,0xdf} {0xa8,0x0} {0xa9,0x0}

value = 0 = 0x0

the customer tried to configure all of the 8 channels of the retimer to 10.3125G, and found that the CDR of 4 channels (0 1 4 5) can be locked (0x78 is 0x30), and the CDR of the other 4 channels (2 3 6 7) cannot be locked (0x78 is 0x20). The connection method of the 8 channels is shown in the figure above. Why the CDR of these four channels (2 3 6 7) cannot be locked? The customer bypassed the CDR of these four channels (2 3 6 7) and looped them back at the optical port. The 25G rate 12H PRBS31 test showed no bit errors, indicating that the hardware link should be ok. The configuration is as follows: 0xfc is the register address, and 0x01 is the data written to the register. The others are similar. At this time, the optical modules have been changed to 10G, and CTC7132 is also configured to 10G mode.

fdd_hal_iic_write_debug 0xf,0xfc,0x01,1

fdd_hal_iic_write_debug 0xf,0xff,0x03,1

fdd_hal_iic_write_debug 0xf,0x0a,0x0c,1

fdd_hal_iic_write_debug 0xf,0x2f,0x04,1

fdd_hal_iic_write_debug 0xf,0x31,0x40,1

fdd_hal_iic_write_debug 0xf,0x1e,0xe3,1

fdd_hal_iic_write_debug 0xf,0x3d,0x8a,1

fdd_hal_iic_write_debug 0xf,0x3e,0x40,1

fdd_hal_iic_write_debug 0xf,0x3f,0x40,1

fdd_hal_iic_write_debug 0xf,0x0a,0x00,1

we discussed this issue on E2Echina, the basic comments is that: both he RX side signal quality and TX configuration error may cause the CDR to fail to lock. the below is the E2ECHINA link:

But the customer is in hard urgency to fix the issue due to project demand, would you please help to have a look of the issue and guide the customer to fix the issue ASAP?

thanks a lot!