Part Number: TCAL9539

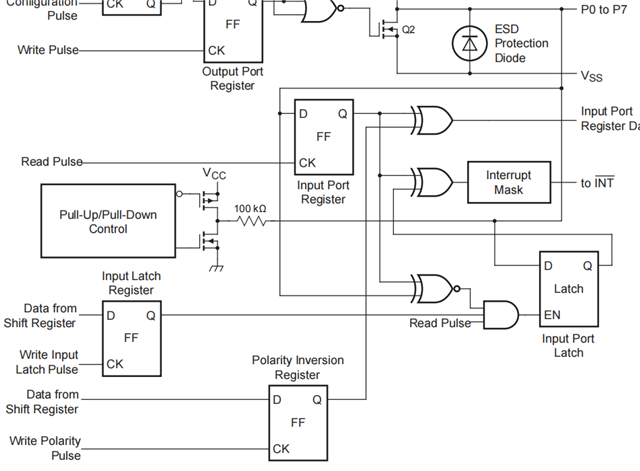

我按照datasheet上的框图搭建了一个仿真电路,其余功能和实际使用下来的芯片功能一致,但是我在仿真时发现框图存在问题:

首先在输入模式读取状态下使能latch,假设latch值为高电平,关闭read pluse,此时input register的Q端为高电平,latch为高电平,不跳INT。改变输入端口的值为0为低电平,无read pluse下input register的Q端仍然为高(锁存触发器),此时latch en端不使能Q端仍然为1,因此无论外部如何改变输入端口的值,INT端都不会跳高,并且在latch register无使能状态下也是一样。这样看的话是不是这个框图是有问题的?