Part Number: ISO1540-Q1

Hi

目前我们这边在使用 ISO1540-Q1做为I2C隔离芯片出现通讯不了的问题,

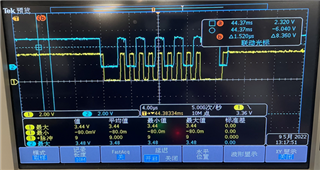

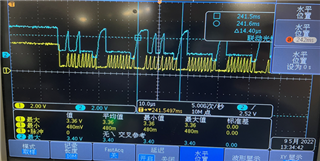

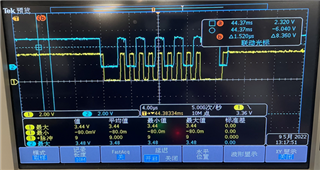

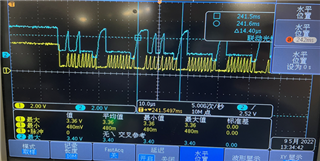

如下是测试数据,左侧为隔离前波形,右侧为隔离后波形,波形失真,请帮忙找技术分析下,导致这个问题的可能原因,及相应对策。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: ISO1540-Q1

Hi

目前我们这边在使用 ISO1540-Q1做为I2C隔离芯片出现通讯不了的问题,

如下是测试数据,左侧为隔离前波形,右侧为隔离后波形,波形失真,请帮忙找技术分析下,导致这个问题的可能原因,及相应对策。

您好,

很可能是总线上的负载电容太大或者上拉电阻值太大的缘故造成的,建议减小上拉电阻值,看输出波形是否改善?I2C上拉电阻值具体计算方法,请参考下面文档第2部分:

I2C Bus Pull-Up Resistor Calculation:https://www.ti.com/lit/pdf/slva689

请问下,目前不加隔离芯片波形是ok的,那是不是说明和上拉电阻值关系不大;

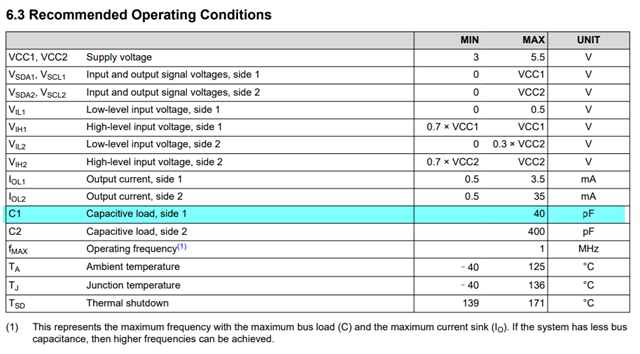

这个主要是与芯片的容性负载驱动能力决定的,ISO1540-Q1 1侧的电容驱动能力最大是40pF,因此如果1侧总线容性负载比较大,总线高低电平就会形成电容缓慢充放电的上升和下降趋势;如果2侧输出端口容性负载驱动能力比较强,就会出现不加隔离芯片波形是ok的现象;

针对负载电容较大的情况有其他办法,或者可以推荐自身寄生电容小点的I2C隔离芯片可以用吗?

这个负载电容主要是指PCB走线形成的寄生电容(走线越长寄生电容越大)和TP_IIC_SDA_O\TP_IIC_SCK_O信号输入IC的输入管脚处的输入电容,与I2C隔离芯片没有关系。因此,降低总线电容的办法就是减小总线走线长度和选择输入电容比较小的1侧IC。

因为信号的充电时间常数是R和C的乘积,即RC,因此在无法改变C的情况下,降低R也就是上拉电阻,也可以缓解这种上升沿和下降沿充放电的时间,以提高上升沿和下降沿的陡度。您是否尝试了减小上拉电阻值来改善波形?

降低上拉电阻值后波形是怎样的?相比于10.5K的上拉电阻是否有改善?同时我也想了解下电路板I2C的走线有多长?

是否可以断开I2C接收端的IC连接,悬空I2C看下 ISO1540-Q1输出波形是怎样的?

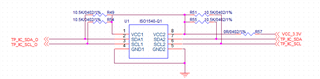

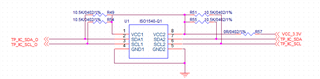

另外, ISO1540-Q1是隔离IC,其两侧的供电电源VCC1和VCC2也需要进行隔离,但在上面电路图中是使用同一个供电电源并没有进行隔离,这其实也失去了使用隔离芯片ISO1540-Q1的意义。我认为这不应该影响I2C的波形,但是您可以使用隔离电源进行验证下吗?看下是否由于没使用隔离电源造成的?注意这里的GND1和GND2也是隔离的

看来应该是走线太长的缘故,ISO1540-Q1 2侧走线长不长?如果不长的话,建议在使用ISO1540-Q1的时候,1侧和2侧接线调换一下,因为2侧的电容驱动能力可以到400pF,比1侧大一个数量级,让其驱动走线长的一侧,效果应该好一些,因为ISO1540-Q1的2个通道都是双向通道。

目前如果可以的话,建议去掉ISO1540-Q1,因为看您的反馈说“不加隔离芯片波形是ok的”,又如我前面所述,ISO1540-Q1其两侧的供电电源VCC1和VCC2也需要进行隔离,若没有进行隔离,就失去了使用隔离芯片ISO1540-Q1的意义