Hello ~

Our system VDD : 5V

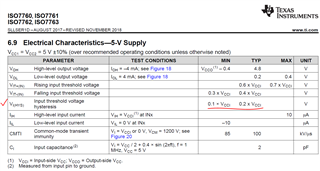

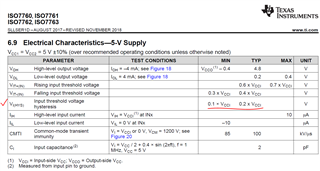

and want to know the “Input threshold voltage hysteresis” define

and explane it

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello ~

Our system VDD : 5V

and want to know the “Input threshold voltage hysteresis” define

and explane it

是的,这是在任何时候必须存在的最小差异。

VIH和VIL是建议的输入电压,而VIT+和VIT-是实际的设备输入阈值。VIT阈值是最坏情况规范,VIT+(max)为0.7*VCC。这告诉客户他们需要应用大于VIT+(max)的输入信号,才能100%的将其视为高电平信号。

VI(HYS)是输入阈值的迟滞,也就是说VIT+和VIT-在任何时候至少会有0.1*VCC的差异。我认为这里可以对比迟滞比较器来理解这个概念。

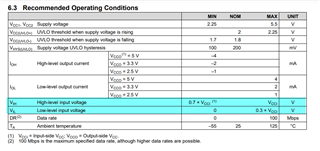

对于Logic high和logic low,我想您应该看 ISO7760 datasheet中的 VIH和VIL参数,VIH最小要大于0.7VCC才能保证所使用的ISO7760 都能保证或100%被视为高电平信号;VIL同样的道理。

VIT阈值是最坏情况下的规范,VIT+典型值是0.6VCCI,输入0.6VCCI的信号可能被视为高电平,但不能保证100%被视为高电平,若要100%被视为高电平,那么输入信号要至少满足0.7VCCI。

请让我知道您是否明白了 ISO7760 datasheet中的 VIH、VIL参数和VIT+、VIT-参数的区别。

我不确定您是怎样定义这个“干扰耐受性”的。对于A牌 ISO 输入信号必须大于0.7VCC才能被识别为高电平,若输入信号受到干扰,可能会降低到0.6VCC,此时A牌 ISO已经不能正常识别为高电平了,而对于 ISO7760其识别高电平的典型值是0.6VCC,此时还有一定概率可以识别为高电平,减小了异常通信的发生,在我看来是干扰耐受性强的表现。