Part Number: SN6505B

Hi Ti Team:

I have a question about the SN6505B chip as follows:

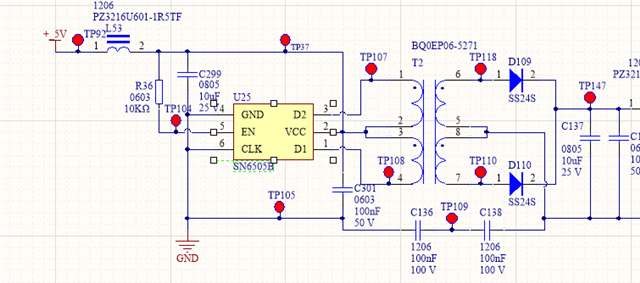

Schematic diagram:

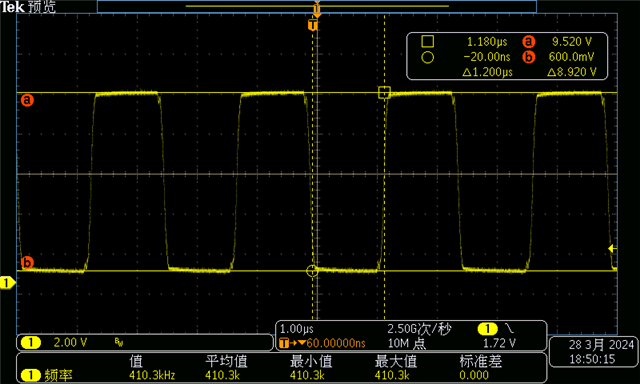

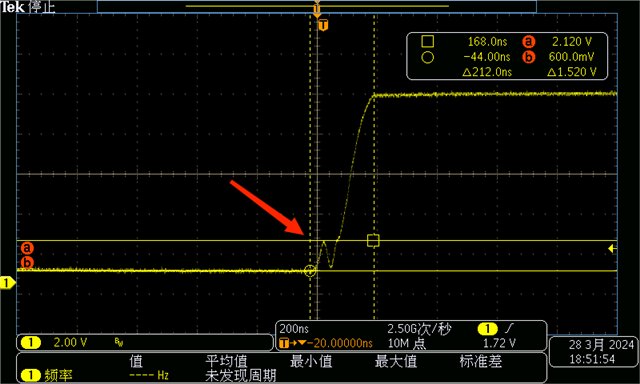

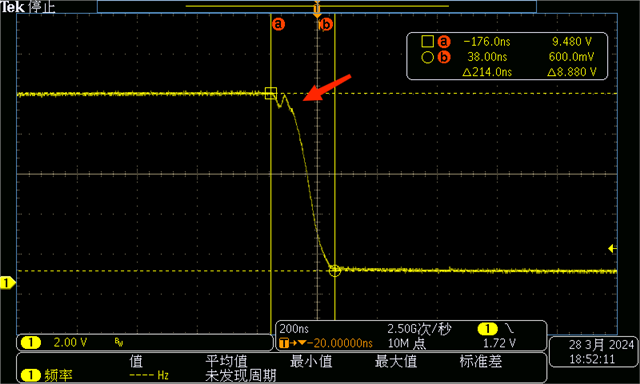

I found that the rising and falling waveforms of the D1 and D2 pins of the actual test chip have a kickback. Is this normal?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好

感谢您对TI产品的关注!为更加有效地解决您的问题,我们建议您将问题发布在E2E英文技术论坛上(TI E2E support forums),将由资深的英文论坛工程师为您提供帮助