Part Number: ISO1228

1. 项目描述

我司使用ISO1228设计了一款产品,验证期间做了4块实物板子(设计是参考EVM User's Guide: ISO1228DFBEVM ISO1228 文档里的原理图制作的),其中2块工作完全正常。

使用的是BURST菊花链模式读取寄存器数据。

1.1 已解决的问题

其中1块遇到位置3的芯片,SDO引脚只能输出高电平(前面两个芯片工作正常,后面两个芯片的8个通道测试接24V信号,LED都正常亮),

用示波器测试4号芯片的SDO,是有数据输出的,更换一个3号芯片后正常(这个板子就当修复了,芯片也没保留做其他测试,扔掉了)。

2. 需要解决的问题

然后又碰到另一块故障板子,这个板子的情况就有点奇怪,大部分情况下:1号芯片寄存器读取也不正常(同样的代码和硬件,3个寄存器读取顺序不正常),后面3个芯片读取都是0,

并且用示波器测试后面3个芯片的SDO引脚,输出都是0。

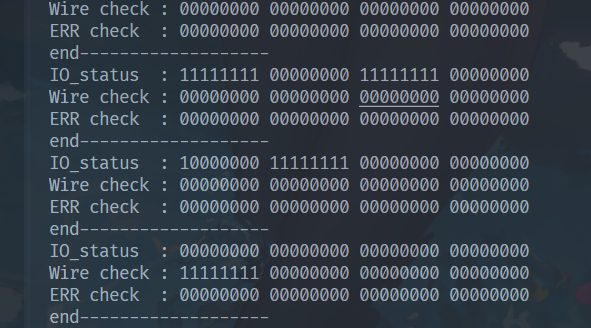

以下是读取到的寄存器数据截图(平时只能读到1号设备的寄存器,但是循序乱,此图为输入通道接入24V信号时,偶尔能读取到23设备寄存器的截图)。

这个故障板子的4个设备,不管是接上任意一个芯片8个通道的其中一个输入通道,LED灯都可以正常亮,并且在接上的一瞬间,有较大几率可以读取到4个芯片的寄存器数据,但是数据也不是正常的。

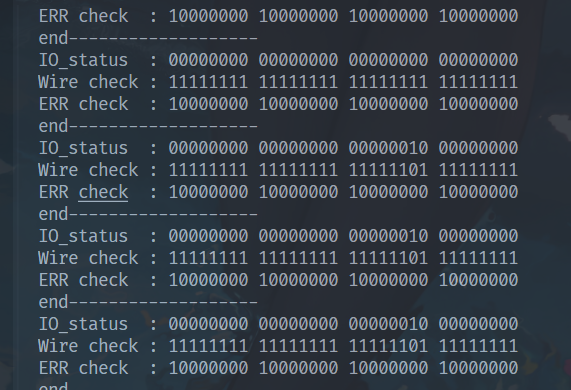

最后附上正常工作板子的寄存器读取数据(代码完全一样,硬件也和故障板子完全一样),代码在MCU初始化的时候,会统一给4个芯片的nSRST引脚(并联、一个IO控制)发出重置信号,

其他信号线参考规格书里的菊花链接线方式。

可以看到正常工作的板子,IO状态可以正常读取,线状态寄存器和错误检查寄存器都可以正常读取。

想问一下,要解决问题,有什么建议和方向?