Part Number: SN74LV165A

您好:

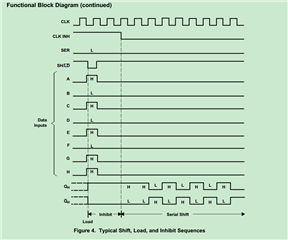

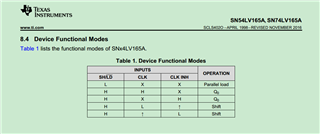

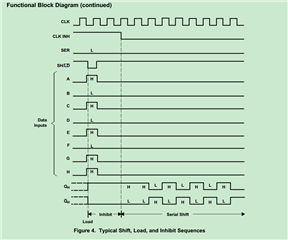

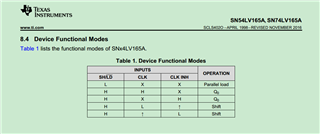

我司一直在使用贵司的一款并转串逻辑器件:SN74LV165A,最近因为产品在现场运行时出现了异常问题,测试过程中顺便测试了SN74LV165A的串行输出信号,发现该芯片在CLK INH信号为高电平时,QH输出电平一直为低电平,而按照数据手册上的真值表和时序图来看,在CLK INH信号为高电平时,QH输出电平状态应该是上一次输出电平状态或者高电平?

请问,该怎样理解?在线急等,谢谢!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: SN74LV165A

您好:

我司一直在使用贵司的一款并转串逻辑器件:SN74LV165A,最近因为产品在现场运行时出现了异常问题,测试过程中顺便测试了SN74LV165A的串行输出信号,发现该芯片在CLK INH信号为高电平时,QH输出电平一直为低电平,而按照数据手册上的真值表和时序图来看,在CLK INH信号为高电平时,QH输出电平状态应该是上一次输出电平状态或者高电平?

请问,该怎样理解?在线急等,谢谢!

您测试异常时,SH/LD是高电平是吧?

建议您用示波器实测各输入信号和输入信号的波形,看信号电平、频率、脉冲宽度以及CLK的上升触发沿等看是否存在问题

您好:

74LV165芯片的SH/LD、CLK、CLK INH几个信号都是按照数据手册上的时序图来操作的,空闲时SH/LD和CLK INH信号都是高电平,CLK信号为低电平,当需要进行操作时:

(1)先将SH/LD拉低装载并行信号,然后在拉高;

(2)将CLK INH信号拉低,并行信号在CLK时钟信号驱动下从QH输出;

(3)数据读完后,将CLK INH信号拉高,并停止输入CLK信号;

该芯片在功能使用上一直没有问题,只是最近测试其它问题时,发现QH输出信号在CLK INH信号为高电平时,输出一直是低电平,这和数据手册上的真值表不一致(CLK INH信号为高电平时,QH输出应该是上一次输出电平状态),而且真值表中说明,只要CLK INH信号为高电平输出信号QH为上一次输出电平状态,和SH/LD信号的电平状态无关系。

请问该怎么解释?