Part Number: SN74HC595

Other Parts Discussed in Thread: CD74HC74

Dear :

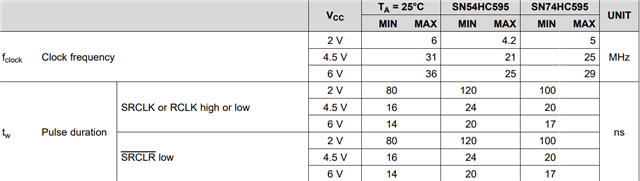

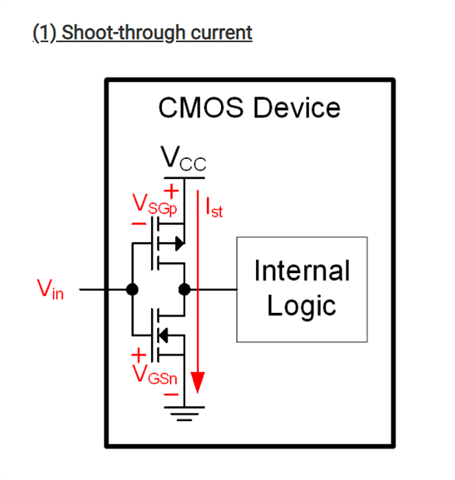

想咨询下问题,SN74HC595串并转换芯片,它的移位时钟引脚SRCLK和锁存时钟引脚RCLK时钟信号,发现串转并出来的数据老是有丢帧,比如我输入串行数据10101010出来的可能就是10100010(可能100次有一次)后来发现是SRCLK时钟上升沿比较缓,2微妙左右,

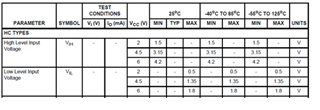

看了下数据手册有个input transition rise or fall time (4.5V供电500ns) 请问这个数据指标是否对输入时钟信号的要求呢?

或者该芯片的输入时钟信号还有其他要求?谢谢