Part Number: TXS0108E

您好,

产品手册关于上拉电阻这个描述,我想问一下这个上拉电阻值切换是内部怎么实现的,这个切换是在高低电平稳定后再实现的吗?

Q2,TXS0108E内部架构图里,MOS上的Bias电压是一直都存在的吗?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: TXS0108E

您好,

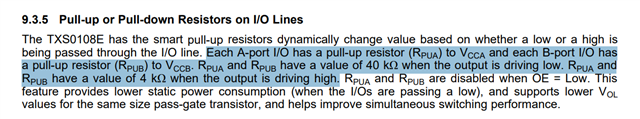

产品手册关于上拉电阻这个描述,我想问一下这个上拉电阻值切换是内部怎么实现的,这个切换是在高低电平稳定后再实现的吗?

Q2,TXS0108E内部架构图里,MOS上的Bias电压是一直都存在的吗?

您好,

1、这个 4 kΩ和40 kΩ应该是指的稳定后的上拉值;

2、不是一直存在的;

具体分析见下面文档的第2部分:

1、这个 4 kΩ和40 kΩ应该是指的稳定后的上拉值;

我考虑的是不是low to high或者high to low边沿触发后就会修改这个电阻值,然后在电平稳定后就是使用这个阻值修改后的电阻值了。不知道理解的是否正确。

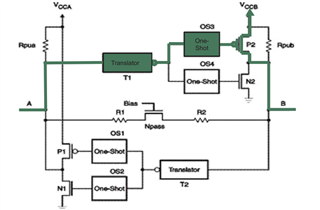

上面这个曲线是 N2 pass-gate transistor的传输特性曲线,Vin是其输入管脚,Vout是其输出管脚,输入不同的VIN电压对应的输出电压。

应该是的,我这样理解的:

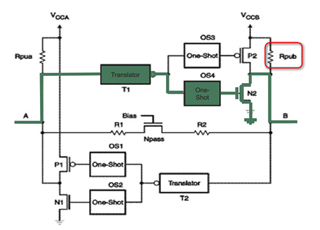

在N2导通输出低时,上拉电阻40kΩ,主要是指下图中的Rpub;

在P2导通输出高时,上拉电阻4kΩ,主要是指下图中的Rpub与P2导通电阻的并联,P2导通电阻相对较小,并联后总值变小。因此输出高电平时,上拉电阻值小,这样改变了上拉电阻值。

下面是我的分析:

NMOS应该不会导通,它的S极接的是GND,但不管它是否导通,其上拉电阻都应是Rpu;

PMOS它应该会导通,PMOS G极有个反向器,输入高电平信号会反向,这样GS电压是一直小于0的,所以会一直导通,直到下一个状态,也只有这样,上拉电阻的值会减小,变为4kΩ。