Part Number: SN74LVC3G07-Q1

Other Parts Discussed in Thread: SN74LVC1G07-Q1, SN74LVC1G07, SN74LVC3G07

您好,

SN74LVC3G07-Q1这颗芯片可以支持的最大数据通信频率是多少?在SN74LVC1G07-Q1的spec中明确写出其最高支持100MHz,但是SN74LVC3G07-Q1没有任何说明。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: SN74LVC3G07-Q1

Other Parts Discussed in Thread: SN74LVC1G07-Q1, SN74LVC1G07, SN74LVC3G07

您好,

SN74LVC3G07-Q1这颗芯片可以支持的最大数据通信频率是多少?在SN74LVC1G07-Q1的spec中明确写出其最高支持100MHz,但是SN74LVC3G07-Q1没有任何说明。

很抱歉,现在才回复您的问题!

SN74LVC3G07-Q1是一款同向buffer,Buffer没有时钟输入,因此没有工作频率参数,但最大工作频率可以通过在同一逻辑系列中找到一个时钟设备来估计。具体见FAQ:[FAQ] What is the maximum data rate (or operating frequency) for a logic gate or buffer?

但SN74LVC3G07-Q1这个buffer是OD输出,因此其实际工作频率达不到同一逻辑系列中的时钟设备。因为其输出高电平时需要接上拉电阻到电源,在设备输出高电平时会有一个RC充电时间,这里的R就是上拉电阻值,C是输出线上的总电容(包括寄生电容和接收端的输入电容等),如果工作频率特别高,那么输出高电平可能达不到接收设备可以识别的电压就又变为低电平输出了,这就造成接收端识别不到高电平。因此实际的工作频率由RC充电时间常数决定。

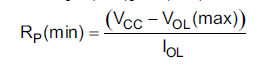

另外,上拉电阻也不能太小了,否则的话,设备输出低电平可能会拉不到很低,即输出的VOL会升高,会使得接收端识别不到低电平,最小的上拉电阻可使用下面公式计算: