Part Number: TCA9803

Hi experts,

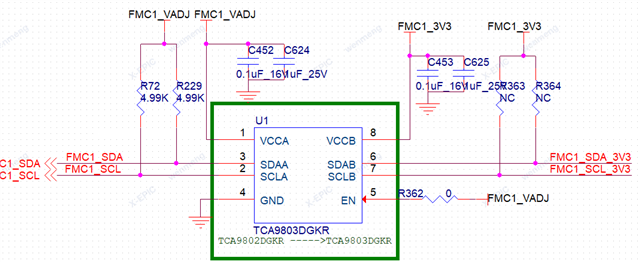

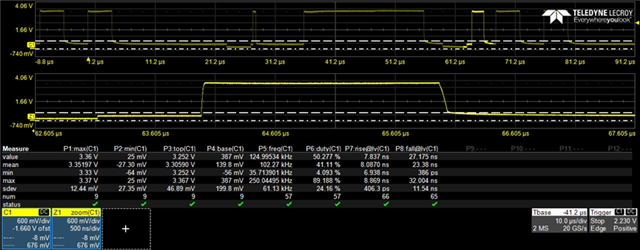

我设计中采用了TCA9803这颗芯片,但输出端B的低电平低不下去,会有个六百毫伏的电压,电路图和波形图如下所示,请问可能是什么原因导致的呢,可以怎样优化?谢谢!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好,电路没问题,由于B端内部集成了电流源,所以外部不需要再上拉。

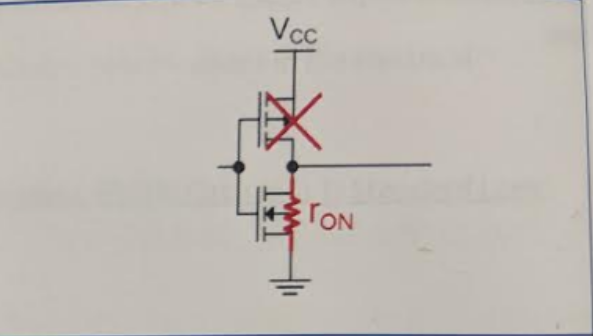

您目前测试的Vol=600mV,看起来像是如下结构,当输出低电平时,MOSFET导通压降0.6V,但事实上TCA9803数据手册上描述并不是PASS FET的方案,作为buffer,能保证其输出Vol约为0.2V的低压。

您是在哪儿购买的? 是否在TI官网上购买?

3.3V的话电平的最高值为0.3 VCC=0.99V,虽然满足低电平的阈值,但是我想还是要尽可能低减少通讯异常问题。

您这是A side到B side,B side低电平拉不下来是吧?如果B side到A side呢?

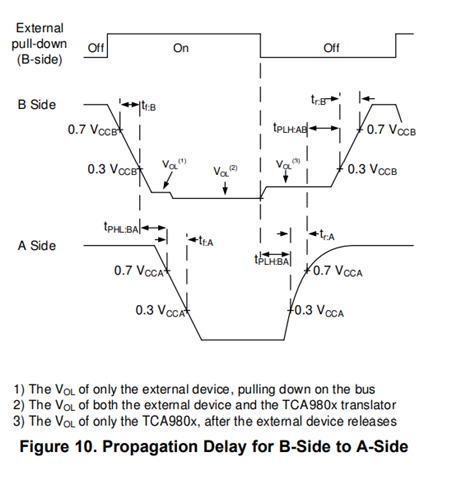

抱歉上周请假了,回复晚了,这里有个突起或者台阶是正常的,参考TCA9803数据手册的Figure10的部分。

下面备注了三处Vol的情况。第一处是外部device拉的低电平,第二处是外部device和TCA9803一起下拉的结果,第三处是当外部device释放之后,TCA980x拉的低电平。