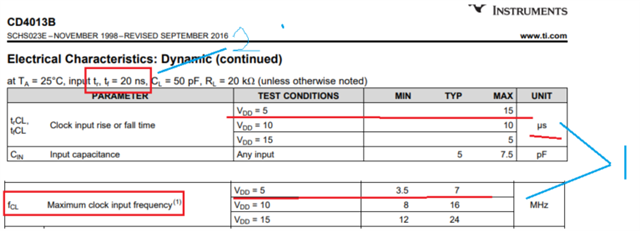

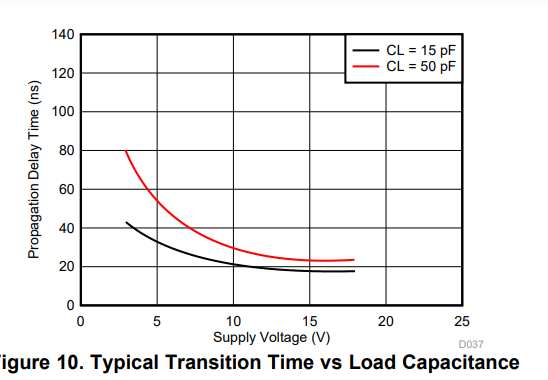

Part Number: CD4013B

您好,

有一个关于Clk上升沿时间的疑问,请支持,谢谢。

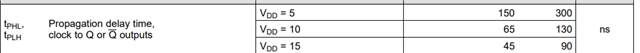

CD4013B供电电压为5V:

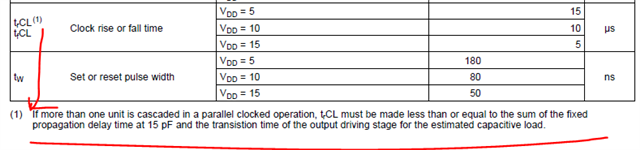

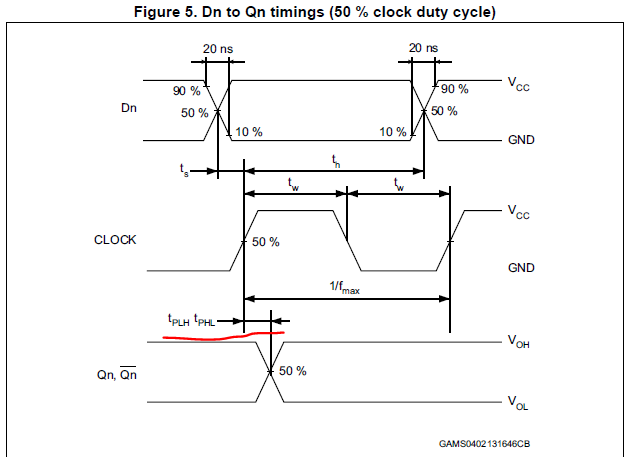

1.从CD4013B的规格书中可以看到trCLmax=15us,这里的trCL指的是Clk从0升到1的时间吗?如果是的话,那和fCL的频率范围有点矛盾呀。如果按照trCLmax=15us,那CLK的时钟频率最快频率=0.3MHz,达不到7MHz啊,是我哪里搞错了?

2.为啥规格书里面trCLmax=15us,而tr=20ns,这两个参数是同一个参数吗?如果不是trCL和tr分别代表啥信号的上升沿?