Part Number: TXS0108E

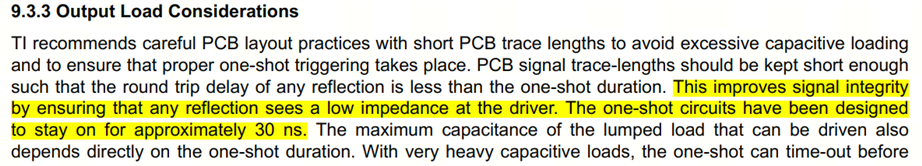

请问一下,TXS0108标注支持Push pull速率最高到110Mbps。但是根据手册实际描述,one shot模块的稳态时间为30ns,在30ns时间内,其控制的MOS管会保持打开,那么理论上来说如果速率超过33Mbps(数据脉宽小于30ns),不就会出现上下MOS管同时导通的情况吗?以及速率超过66Mbps时(数据脉宽小于15ns),上下管永久导通的情况出现。所以请问这个速率实际是怎么计算的,与这个30ns的one shot稳态时间存在矛盾吗?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好,通常我们使用传输延迟tpd(+10%)的倒数来估算这类器件的data rate,判断器件是否能支持信号速率的时候,如果实际信号的data rate远小于根据tpd计算的速率,那么肯定是支持的,尽量是留有一定的余量。

影响data rate有很多因素,比如输入信号的敏感度,输出边沿速率等。

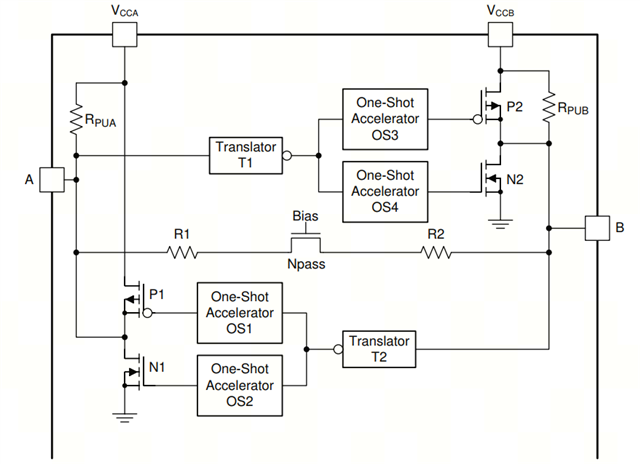

TXSxxx的原理内部是one shot电路, 在开关期间(根据 VIH 和 VIL 电平)在大约30%至50% Vcc 的范围内检测到上升/下降沿,会激活one shot 电路,从而将输出短接至 VCC 或接地以实现高电平或低电平的切换。具体工作原理我们可参考这篇TXS电平转换的user's guide:

您好,抱歉回复晚了。

按照您的推论,确实P2和N2会同时导通出现死区,那就无法规避了。

可事实上是,我们无法准确的确定one shot是什么时候开启,什么时候关闭的。

理论上应该是,当one shot持续稳态时间结束之后,当检测到输入上升沿时,P2导通,输出为高电平,当检测到输入下降沿时,N2导通,输出跟随输入为低电平。

您好,

还要考虑一些其他因素,比如Translator模块的delay以及数据的rise/fall time,同时保留一些设计裕量,实际数据速率是会远远低于手册100Mbps吧?

您考虑的很全面,data rate确实和很多因素有关,比如您提到的delay,rise time /fall time. 所以我们如果根据delay 的倒数计算出来的值其实是偏小的,但是对于TXS0108来说,可以支持的Push pull和open drain的速率,已经把这些因素考虑进去了,push pull能支持到110Mbps,实际也是能支持到这个速率的。