Part Number: SN74LVC1G175

在论坛中另外一个类似的问题是由于上下延时间太缓导致,但是clr后还在下降沿触发输出Q0?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

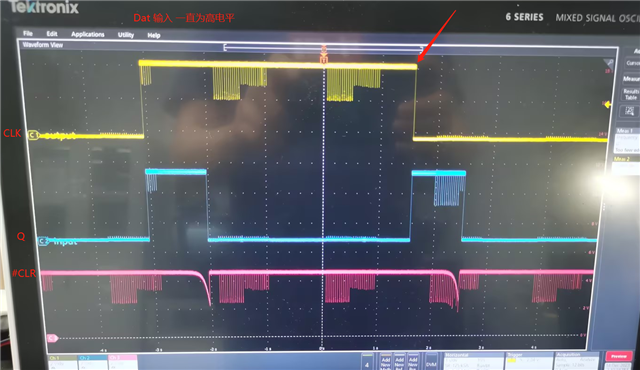

通过这个波形来看,CLK的上升沿和下降沿都触发,是否有测试输入信号的rise/fall rate Δt/Δv满足datasheet中要求吗?

但是clr后还在下降沿触发输出Q0?

CLK为低电平时,不论CLK为上升沿还是下降沿,输出Q为低电平,直到下一个CLK的上升沿才会改变Q的输出,看您的波形CLR这里没问题的。

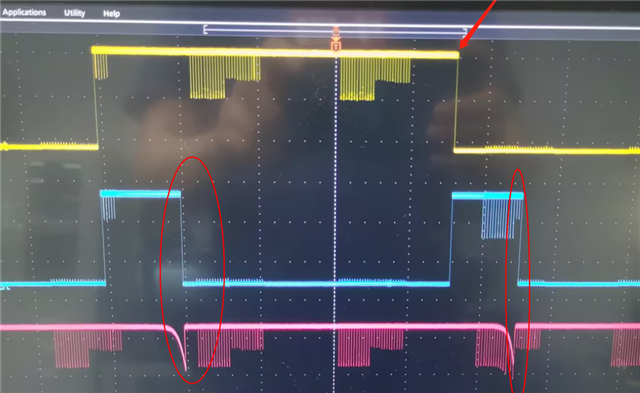

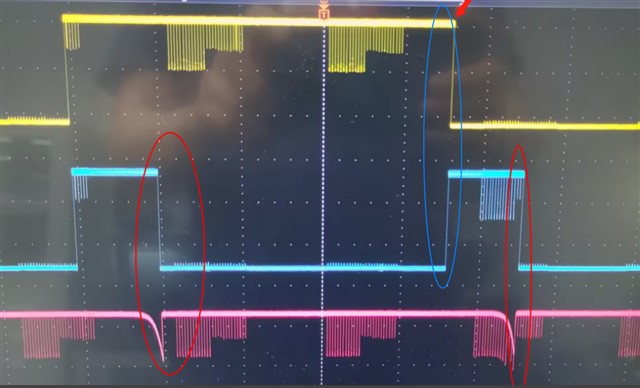

CLR为低电平时,Q输出为低,这个是遵循数据手册真值表的。即红色框的两处,CLR为低,Q输出为低。

您指的CLR触发清除后,也就是第一个红色圈部分,CLR触发清除之后,又从低到高变化了,这时Q的输出应该是按照CLK的上升沿触发,反而在蓝色部分CLK下降沿触发Q输出,所以这里的问题还是为什么CLK的下降沿都触发了输出Q。因此需要验证Δt/Δvt 。

也或者您做下试验,就是CLR一直为高,您看下CLK的下降沿是否触发Q输出?我认为也会的。

是想了解清楚,在CLR触发了清除后,clk下降沿为何会触发Q的输出。