Part Number: SN74LVC2G17-Q1

Other Parts Discussed in Thread: SN74LVC2G17

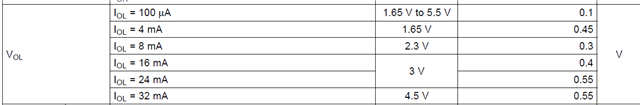

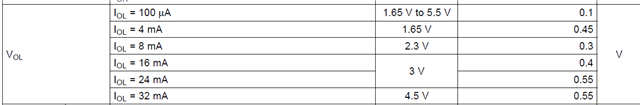

请问这个IOL是什么意思呢,譬如这个buffer芯片输出接的上拉电阻到1.8V,假如需要buffer的输出电压表现为0.1V,那么这个上拉电阻阻值需要>(1.8V-0.1V)/0.1mA=17k 嘛?谢谢

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: SN74LVC2G17-Q1

Other Parts Discussed in Thread: SN74LVC2G17

请问这个IOL是什么意思呢,譬如这个buffer芯片输出接的上拉电阻到1.8V,假如需要buffer的输出电压表现为0.1V,那么这个上拉电阻阻值需要>(1.8V-0.1V)/0.1mA=17k 嘛?谢谢

您好,

是这样理解的。

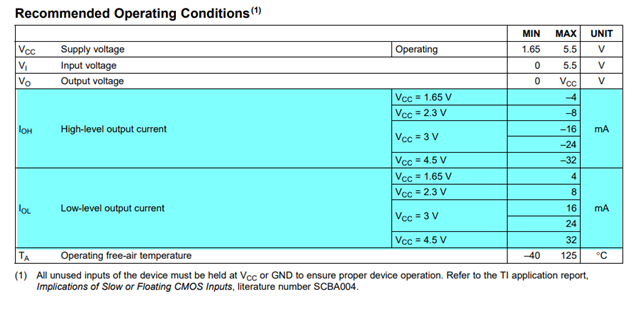

SN74LVC2G17有最大输出输入电流要求,如下截图在不同供电电压下的最大输出输入电流值:

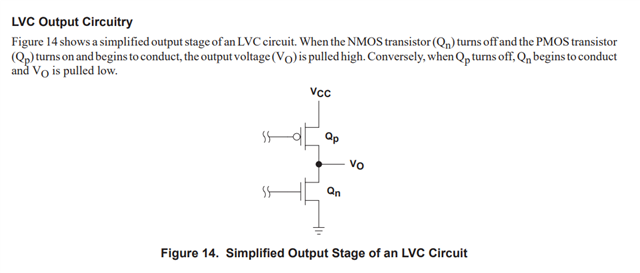

上面您给出的截图VOL参数它其实要表达的是在输出可以输出/输入的最大电流时,SN74LVC2G17的输出电压,因为SN74LVC2G17内部有上下开关管,如下截图中的QP和QN,其内部上下开关管在导通时会有导通电阻,流经的电流在此导通电阻上会产生压降,也就是说电流越大,这个压降越大。当输出低电平时,是输入电流,那么就会在下管QN产生压降,电流越大,压降越大,输出电压VOL就越大。输出高电平时同理,输出电流越大,压降越大,输出电压越小。

在输出低电平时有灌电流,那么这个灌电流需要小于我上面截图中参数。您选择灌电流0.1mA,也是可以的满足上面最大参数,且灌电流越小,输出的VOL越小。

希望以上解释清楚您的疑问。

Amy 姐姐,

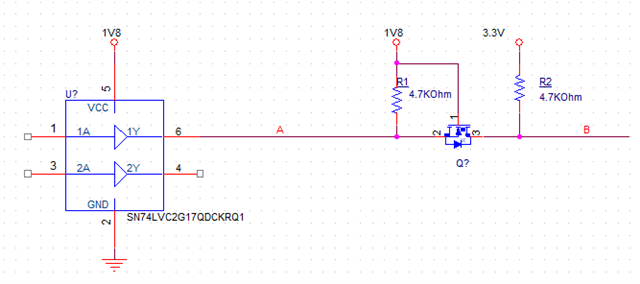

我以我们实际应用再请教一下:假设NMOS的Vth=1.7V,那么我如果想NMOS能完全打开,那么SN74LVC2G17QDCKRQ1输出的VOL要小于0.1V,那么此时R1的电阻阻值是不是需要大于(1.8-0.1V)/ 0.1mA=17K?0.1mA对应SN74LVC2G17QDCKRQ1输出VOL最大0.1V时的电流。

此时NMOS导通,3.3V电压又会通过R2(假设R2的电阻较小)——>NMOS,与1.8V——R1的电流之和灌到SN74LVC2G17QDCKRQ1里,此时电流就大于0.1mA了,那会不会导致VOL超过0.1V,从而VGS《VTH,NMOS又不导通呢?

假设NMOS的Vth=1.7V,那么我如果想NMOS能完全打开,那么SN74LVC2G17QDCKRQ1输出的VOL要小于0.1V,那么此时R1的电阻阻值是不是需要大于(1.8-0.1V)/ 0.1mA=17K?0.1mA对应SN74LVC2G17QDCKRQ1输出VOL最大0.1V时的电流。

是的,是这样理解的。

此时NMOS导通,3.3V电压又会通过R2(假设R2的电阻较小)——>NMOS,与1.8V——R1的电流之和灌到SN74LVC2G17QDCKRQ1里,此时电流就大于0.1mA了,那会不会导致VOL超过0.1V,从而VGS《VTH,NMOS又不导通呢?

需要说明的是这个0.1V的VOL是在此测试条件下的最大电压,它是满足所有器件的指标,因此有些器件的这个VOL会小于0.1V,所以严谨的说,您这个情况可能会导致NMOS又不导通。如果R2足够小,那么就会导致NMOS又不导通。