Part Number: CD4013B

您好:

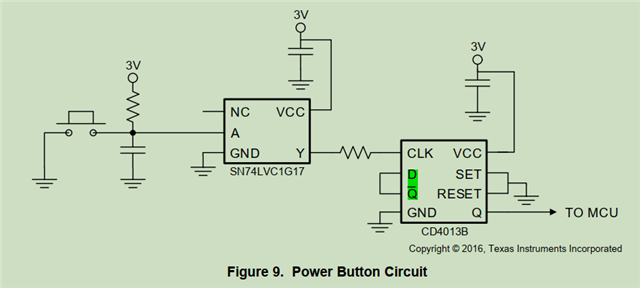

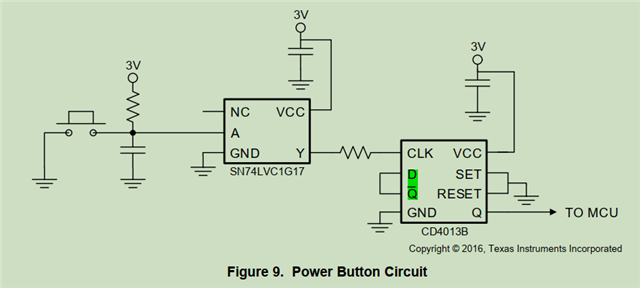

请问下面这种图,将D和Q反连接到了一起,那D的电平是高还是低啊?我最近改以前同事的电路(我们也是电源按键类的),看到他这里也是这样连接的,但不太理解。

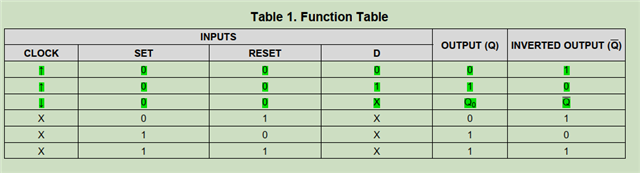

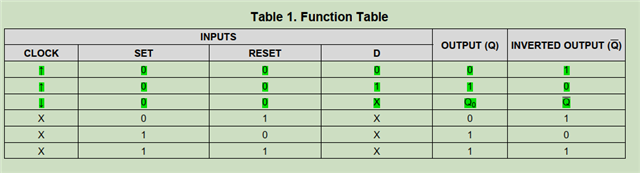

按照下面的真值表,按键按下后,4013芯片的CLK上升沿,然后Set和reset都是0,但是D的电平是啥呢,因为它跟Q反连接到一起了呢,而Q反是个输出啊。

非常感谢。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: CD4013B

您好:

请问下面这种图,将D和Q反连接到了一起,那D的电平是高还是低啊?我最近改以前同事的电路(我们也是电源按键类的),看到他这里也是这样连接的,但不太理解。

按照下面的真值表,按键按下后,4013芯片的CLK上升沿,然后Set和reset都是0,但是D的电平是啥呢,因为它跟Q反连接到一起了呢,而Q反是个输出啊。

非常感谢。

您好,

看下面FAQ,它是没有默认输出的,有可能是高有可能是低电平:

[FAQ] What is the default output of a latched device? (Flip-Flop, latch, register)