Part Number: TXB0108

Hi TI同事:

请教下,

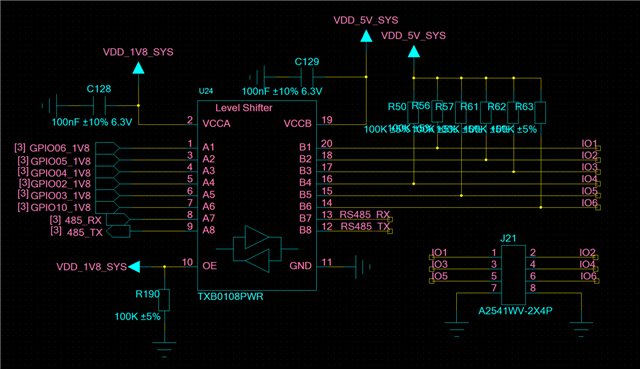

问题:测试发现B侧IO的上拉电阻值改变会影响到A侧IO的电平状态,导致B侧IO电平无法跳变。(A侧IO接MCU配置为输入上拉1.8V)

使用场景:B侧6个IO有上拉电阻到VDD_5V_SYS,并通过J21到按键;A侧IO接MCU,配置为输入上拉1.8V并捕获按键的低电平。

上电时序:VCCB(VDD_5V_SYS)先上电,VCCA(VDD_1V8_SYS)后上电。

测试1:移除TXB0108,单独测量A侧6个IO,均为1.8V高电平,未发现MCU有拉低IO动作。

焊上TXB0108,R50-R63为100K时,VCCA上电,B侧IO会输出0.15V左右电平(像是A侧IO被拉低,导致B侧VOL为0.15V)

测试2:在问题1基础上,修改B侧上拉电阻为50K,VCCA上电,B侧IO会输出0.35V左右电平(像是A侧IO被拉低,导致B侧VOL为0.35V)

测试3:在问题1基础上,修改B侧上拉电阻为10K,VCCA上电,B侧IO会输出1.5V左右电平(像是A侧IO被拉低,导致B侧VOL为1.5V)

测试4:在问题1基础上,修改B侧上拉电阻为1K,VCCA上电,B侧IO会输出正常5V左右电平(B侧IO 1K上拉好像不会对A侧IO产生影响)

SCH如下:

还请帮忙看看上述现象的大概的原因,或是设计哪里有问题,谢谢!