Other Parts Discussed in Thread: TINA-TI, TLV9351

主题中讨论的其他器件:Tina-TI、 TLV9351

工具/软件:

您好、

我尝试在设计中添加右腿驱动、并有几个问题。 我得到的概念很好,但我在网上看到的大多数论文/文档/文章/视频从多个来源没有解释所有的组件或我如何计算适当的值,所以我仍然有一些未知。

注意:许多 DRL 的演练/派生会从两个缓冲器的输出获取共模信号、因为这足以从概念上演示内容。 我不希望从分立式运算放大器制作自己的 INA、因此、以下所有内容都适用于使用来自外部增益电阻器的共模信号来实现 DRL。

1) 增益电阻网络。

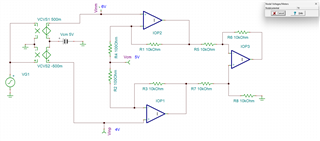

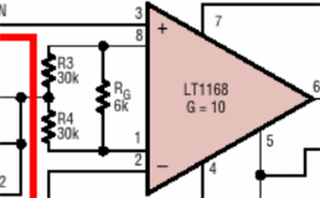

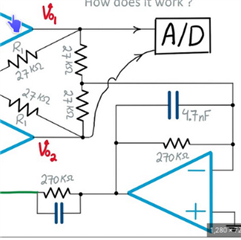

在一些设计中、我看到分接两个增益电阻器上的共模信号:

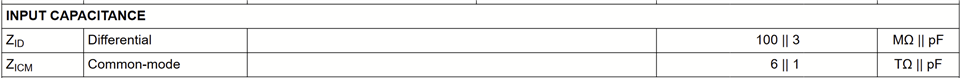

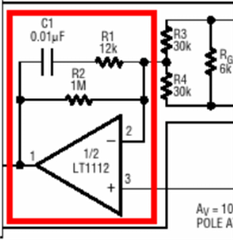

其他设计还添加了第三个与这两个器件并联的电容器:

有人能解释一下第三个电阻器的原因吗? 它只是为了元件匹配/容差、还是与在反相放大器之前使用缓冲器有关? 如何为下游放大器和 INA 的适当增益选择合适的值?

2) 使用缓冲器

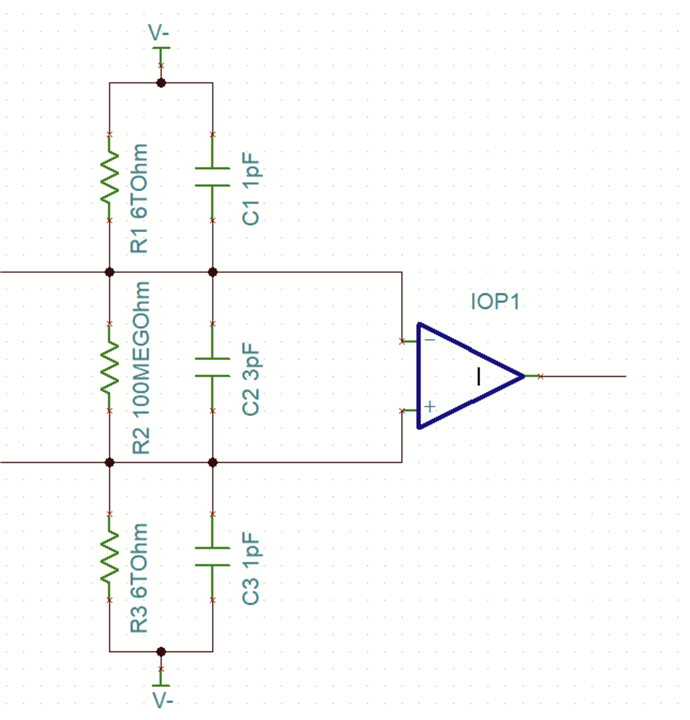

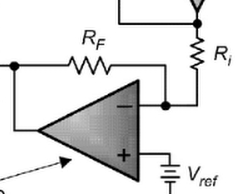

一些设计将抽头的共模信号直接馈入反相放大器:

其他设计在反相放大器前面有一个缓冲器:

这种方法有哪些优点? 是为了防止反相放大器中的任何不稳定因素重新进入 INA 中的共模信号吗?

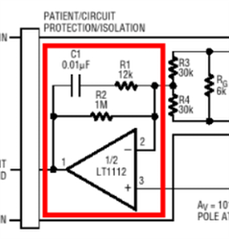

3) 过滤

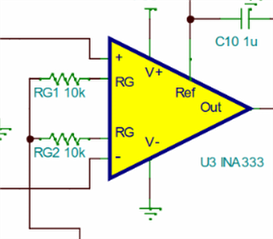

基本设计只需使用电阻器网络来设置反相放大器和短路保护电阻器的增益:

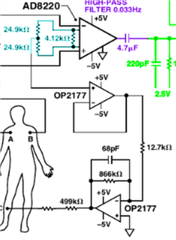

其他滤波器包括低通滤波器和稳定滤波器:

我看到其他人使用高通滤波器(?) 太多:

我的基本理解是、滤波器无论如何都要抑制信号通带之外的高频噪声。 此外、由于大多数 INA 的 CMRR 较低且高于~10-20kHz、因此我们应该忽略该范围。 如果我仍然在放大器输入端进行滤波、那么我不应该尝试将其反馈回。

低通的转角频率是否应该与我的输入滤波器大致匹配? 即、RFI 滤波器的–3dB 频率约为 45Hz、因为我使用的是 EEG、并且任何高于该值的噪声都超出了应用的范围。 我是否应该在逆变器上滤除大致相同的频率范围?

然后、我假设稳定部分是为了防止反馈网络中出现谐振、我们需要在使用负反馈时抑制信号、因此输入端共模信号中的脉冲可能会导致 DRL 电路来回剧烈振荡。 是否有关于如何为此计算适当值的指南、或者我是否可以在使用运算放大器时使用有关衰减负反馈环路的通用参考? 我以前在其他场合见过共振的概念,但没有专门在电子产品中看到,所以我想我可能可以查找一个通用电路模板并使用它 — 但它的 soe 可能会让我稍稍作了解、我不确定这里是否需要考虑一些特殊注意事项。

是否有人能够帮助我或在这些问题上指出正确的方向? 或者、您是否知道有关如何选择实现 RLD 子电路的具体细节的任何资源? 由于我找到了许多有关概念的指南、但在我对电子产品的理解程度较低时、我一直在努力将其转换为我可以使用的特定原理图。

非常感谢您的帮助!!