Other Parts Discussed in Thread: THS3217, THS3491, BUF802, OPA140

主题中讨论的其他器件:THS3217、 BUF802、 OPA140

工具/软件:

您好、

我想知道电流反馈放大器 THS3491 是否可以配置为 D2S、如 THS3217? 如何进行选择呢?

Weyann

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的 Weyann:

可以将 THS3491 设置为差分放大器配置、该配置将是电路的 D2S 部分。 对于缓冲输入级、您也可以在 1V/V 增益下使用 THS3491、但可能还有其他选项、因为大多数增益为 1V/V 的电流反馈放大器都需要进行一些调整、因为它们往往在更高增益下表现更好。 一般而言、我认为 THS3217 中的每个阶段都可以使用 THS3491 独立复制。 实施该电路时、主要考虑因素是确保反馈电阻在所用增益和封装相适应的理想范围内。 表 9-2 建议使用应用于一些增益配置的反馈电阻器。

此致、

Ignacio

尊敬的 Weyann:

我想补充一点、THS3491 型号的设计只能在 5V/V 的增益下工作 为了更准确地表示该器件的性能、数据表将是您的理想基准。 但是、正如我提到的、我看不到该器件无法用作 THS3217 分立式版本的原因。 我还想补充一点、如果将该器件或任何电流反馈器件视为缓冲器、则需要一个反馈电阻器来保持器件稳定。 对于 THS3491、我们建议在增益为 1V/V 时保持约 2100 Ω

此致、

Ignacio

尊敬的 Weyann:

此带宽是否需要特定的峰峰值? 这是一个非常宽的带宽要求、尤其是当仅考虑平坦区域时、可能是寻找工作器件的困难部分。 此外、纵观 BUF802 电路、我很好奇您是否在器件输出端看到预期结果。 添加了 10M Ω 电阻器和电容器的输入结构(例如 C5 和 C6)应该会改变不同频率下的响应、因此我很好奇您是否可以在整个频率范围内获得平坦的响应。

此致、

Ignacio

我们构建并测试了该设计、带宽约为 3dB 压降下的 230MHz。 R1、R4 和 R9 是 10:1 分压器、C5 和 C6 用于增加输入电容、这使我能够与 VR1 电容器复合。 我只会安装 C5 电容器并使 C6 保持开路状态达 10:1 分压器。 我还注意到 VR3 没有什么帮助、我应该删除它吗? 我需要将其设计到 3X1.2 英寸 PCB 上、尝试限制我使用的器件数量。

尊敬的 Weyann:

230MHz 是否在 BUF802 电路的输出端捕获? 您是否在测试中看到了干净的信号。 我想知道阻抗匹配是否会导致带宽问题。 我们必须调整输入级、以确保在整个频率范围内保持 50 欧姆的输入阻抗。 对于 VR3、假设它也是电位器、我们将其纳入来调整交叉区域 、在该区域中、高阻抗路径将从精密路径接管、从而尝试在从直流到 BUF802 将在的高频下获得尽可能平坦的响应。

此致、

Ignacio

尊敬的 Ignacio:

感谢您的答复。 根据数据表、BUF802 将在 1GHz 左右平坦工作、除了 THS3217 和 THS3491 外、我找不到 D2S 运算放大器还可以在直流至 HF 的频率下工作。 我确实将网络分析器连接到电路、它确实在 230MHz 周围表现出良好的平坦 BW、适用于整个电路、而不仅仅是 BUF802 的输出。 该电路板采用 0603 封装设计、元件之间有较大的间距。 我同意、将阻抗路径与滴度布局相匹配可以改进 BW。 这是我的第一种高速 PCB 布局、我正在研究版本 2 布局。 我这次使用 0402 封装、能否根据您对布局布线的经验分享一些建议?

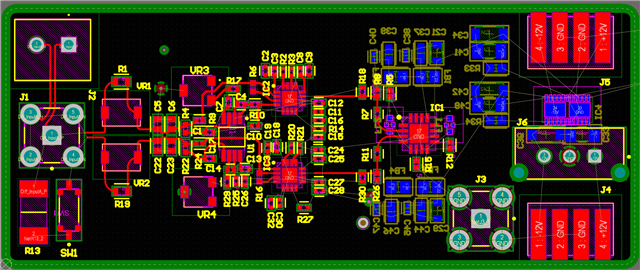

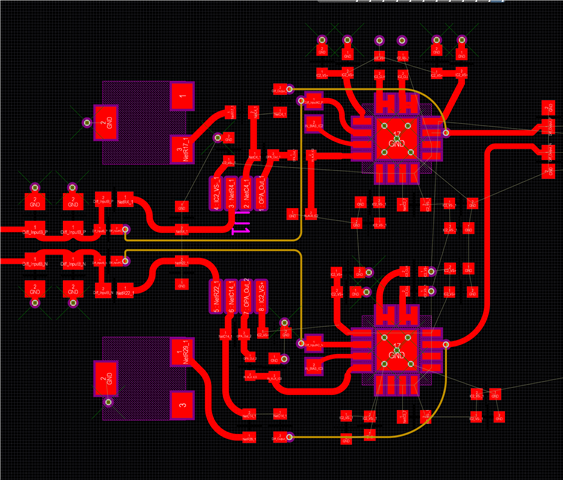

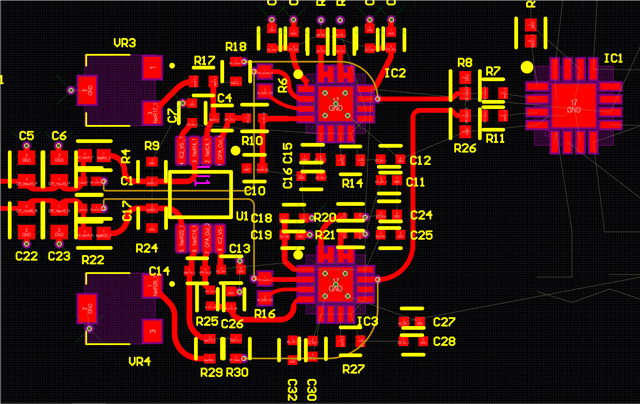

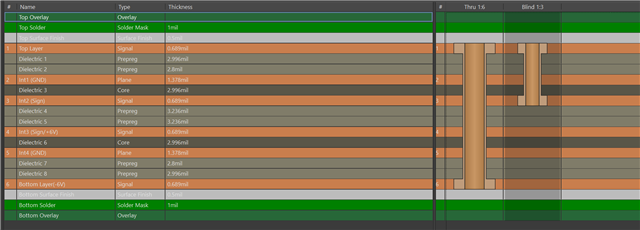

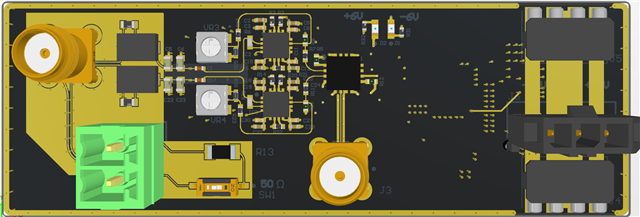

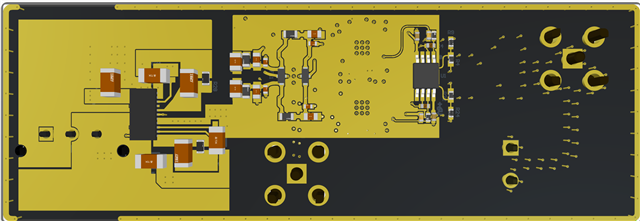

它是 6 层板、FR408 的尺寸为 2.9 X 1.2 英寸。 下面显示了电路板堆叠和布局布线

此致、

Weyann

尊敬的 Weyann:

您能否分享为获取频率响应数据而设置的 Vpp。 如果它是小信号、并且 BUF802 电路中没有限制、则 THS3217 在理想情况下应具有比 230MHz 更好的带宽性能。 如果可能、您是否可以尝试小信号测试(如果尚未尝试)。 对于 BUF802、我们通过调整输入电路以在整个频率范围内进行阻抗匹配来获得 1GHz 的频率。 我很好奇、这是否是带宽性能降低的原因。 查看一下布局。 我有一个问题是关于您的输入、在您的第二个分支(通过 R19)、该输入是我可以看到的 SMA (J1) 正文。 这是否是电路的目的? 我想知道这是否也会导致某种反射、从而导致带宽降低。 我建议将去耦电容器从 0.1pF 调整到 0.1uF、我不确定这个小的电容器是否有用。 我还建议尽可能将去耦电容器靠近电源引脚放置。 理想情况下、包含 C11 的行应移至更靠近引脚的位置。 总体而言、布局看起来确实很紧凑、非常适合处于这些速度的应用。 我建议查看我们针对 BUF802EVM 的布局、因为这将是我们关于如何对该器件进行理想布局的最佳参考。

此致、

Ignacio

尊敬的 Ignacio:

感谢您提供的信息和建议。 我已经使用网络分析器测试了此电路、这将是小信号测试正确吗? 与 10M 电阻器配对的 VR1 和 VR2 是可调电容器。 我添加 C5 和 C22 来增加 BUF802 的输入电容、因此我有足够的空间将电容与 VR1 和 VR2 复合。(C6 和 C23 将为 DNI、以便将来更新 50:1 或 100:1 分压器)我同意 J1 SMA 对与 Molex J2 将引起反射、Molex 用于双绞线电缆。 您是否有建议 或连接器可以改善阻抗问题? 我使用盲孔将 BUF802 的输入和输出信号布线从顶层更改为第 3 层、根据 Altium 阻抗计算结果、布线宽度只能为 3.7mil。 我应该留在顶层吗? 过孔尺寸为 7mil 孔、直径为 11mil、顶部膨胀为 4mil。

此致、

Weyann

尊敬的 Weyann:

是的、正确的、如果您使用某种具有小信号 (~100mV) 的网络分析器、则性能限制不应是 THS3217、因为它的带宽性能明显高于 230MHz。 性能降低可能是 BUF802 电路的输入结构所致。 我假设您正在尝试在两个节点处捕获差分电压;除了使用像您这样的 SMA 进行某种同轴设置之外、我不确定最佳方法是什么。 为了使该电路能够用于高输入阻抗设置、我认为使用电容网络 C5(加上任何寄生效应)来调整 VR1 必须非常精确、才能获得正确的响应。 您是否注意到在调整 VR1/VR2 时、带宽会发生显著变化、无论它是提高还是进一步降低? 这将有助于我们了解带宽性能是否由电路的这一部分引起。 对于布局、我们尝试限制任何过孔到不同层的布线、因为这对于高速信号而言并不理想。 然而、我们确实通过了连接到 OPA140 的布线的反馈部分、但使反馈网络保持在靠近 BUF802 的输出端。 对于进入 BUF802 的信号、我建议将其保留在顶层、并尝试使其尽可能靠近输入端、因为额外的布线长度也会产生电感。 我连接了 BUF802EVM、以供参考、说明我们如何布置该电路板。

此致、

Ignacio

尊敬的 Ignacio:

对不起,延迟回复,我重新布局和缩小板尺寸到 1 x 3 inchs。 我遵循了您的上述建议、并将所有 HF 布线布置在顶层。 如果不进行正确调优、VR1 和 VR2 将影响频率响应。 我们必须手动校准每个误差源。 如果此布局/设计效果很好、我想尝试具有边缘卡的数字电容器设计。 我想使用软件自动校准。 最后、您能看一下我原理图上的 THS3217 吗? 有什么我遗漏的吗? 谢谢你。

此致、

Weyann

尊敬的 Weyann:

我能够浏览您的 THS3217 原理图、我有几个建议。 我相信对于 VMID_IN 引脚、如果不使用缓冲区、可以将其保持悬空。 可以移除 R5、这有助于减少电路所需的任何空间。 同样的思路也适用于电阻器 R12、因为您不会使用该路径。 对于输入引脚、是否需要将 50 Ω 电阻器接地? (R8 和 R26) 我们的电路板上装有这些电阻器、以便与前一级的 50 欧姆串联电阻器实现阻抗匹配。 如果一切都在单个 PCB 上靠近在一起、则您不需要阻抗匹配、在这种情况下、缓冲器通过将这些电阻器接地来驱动较重的负载。 R7 和 R11 应正常。 对于 pathsel 引脚、我会考虑 将该引脚设置为高电平、这可能导致 D2S 级的输出转到引脚 9 并使引脚 9 悬空。 我不确定禁用 OPS 的同相输入会如何工作、为了安全起见、最好将此 D2S 输出设置为引脚 9、因为它无论如何都处于悬空状态。

此致、

Ignacio