主题中讨论的其他部件: Strike

工具/软件:

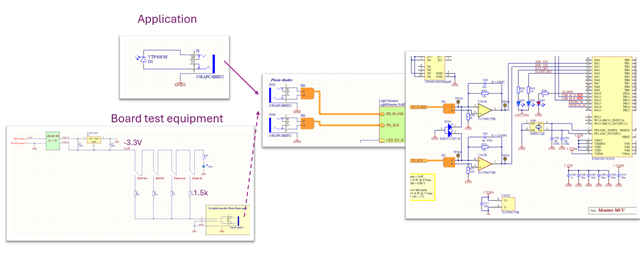

我正在调查两块通过了电路板测试但后来在应用中出现故障的电路板。

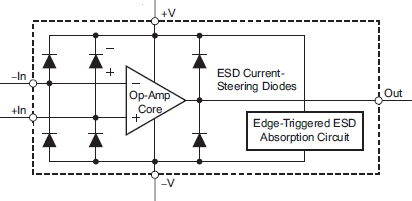

两个电路板上的 TLV9062 均损坏。 它会使电路板的正电源轨短路。 此外、在移除后、连接至 GND 的运算放大器之一的所有引脚之间只有几欧姆的电阻。

该芯片用于光电二极管的 TIA 配置。

在电路板测试期间、通过串联电阻向负输入端施加负电压、以模拟光电二极管。 使用的最大电流为 2.2mA。 根据数据表的解释、只要电压限制为低于 10mA、就允许电压超出电源轨。 我理解正确吗? 当电路未通电时(两个电源轨都为 0V)、情况也是如此吗?

在两个电路板以相同方式发生故障的应用中、输入连接到光电二极管 VTP4085H、短路电流低于 1mA。

您能看到解释这些故障的设计缺陷吗? 光电二极管/测试设备可能在电路板未通电时处于活动状态。 另外、连接光电二极管的电缆在二极管本身未连接时也存在。

我附上了应用和电路板测试的原理图。