Other Parts Discussed in Thread: OPA205, ADS127L21

主题中讨论的其他器件:OPA205、 ADS127L21

工具/软件:

您好、

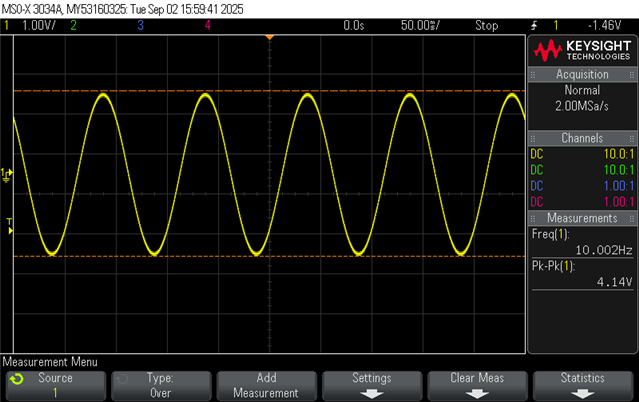

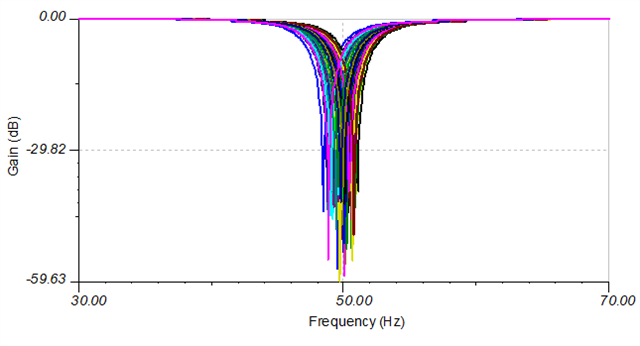

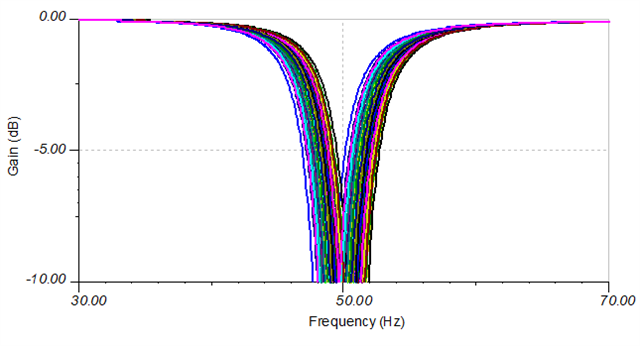

我正在尝试使用 Fliege 拓扑设计一个 50Hz 陷波滤波器。 在我的测试中、每个级都实现了大约 20dB 的衰减。 基于此、我预计在级联三个级时会达到大约 60dB。 但是、将它们合并后、我只能看到大约 23dB。

在两个级之间、我添加了电压跟随器电路。 每级的 Q 系数为 10。 该设计在仿真中表现良好、但在实践中、我无法获得预期的结果。

附加了每个 Fliege 滤波器级的电路图。 元件值为:

- R1 = R2 = 300kΩ

- C1 = C2 = 220nF

- R3 = R4 = 14.5kΩ

- R5 = R6 = 1kΩ

对于可能导致此问题的原因、我非常感谢您提供任何指导或建议。