Other Parts Discussed in Thread: OPA2328, OPA3S328

主题中讨论的其他器件: OPA3S328

工具/软件:

您好、专家、

我的设计使用 OPA2328 本质上是作为低驱动强度 15MSPS DAC 的“负载隔离“电压跟随器、因为它具有良好的规格和注明“单位增益稳定性“的数据表。 遗憾的是没有时间进行 EVK 测试或大规模电路板、因此我们需要采用紧凑的焊盘中孔电路板设计、才有机会实现演示死线。

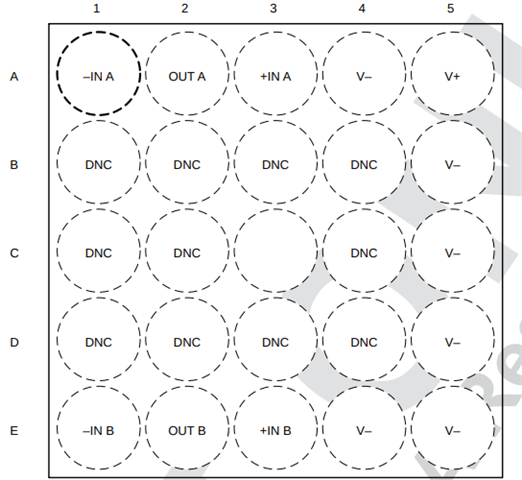

现在我们看到、如果我们将一个整洁的 500mVpp 正弦馈入焊球 E1 的“+in A“、将 500mVpp 余弦馈入焊球 E3 的“+in B“(在应用板上的馈入电阻上测量)、则焊球 A2 上的“out A“直接穿过焊球 A1(“-in A“)、焊球 E2 上的“out B“从封装排布、返回到硬焊球 A3“输出、 从 0V 至 3.3V 电源轨完全摆动、无法找到正弦。

在外部光学检测 中、芯片的对齐情况似乎是正确的:与功能相比、似乎所有芯片都放置在同一位置、以便其中间与封装中的“漏球“对齐。

芯片上的点标记出现在封装上的 A1 焊球上、数据表似乎强烈暗示这是正确的(也是标记 BGA 的唯一合理方法)。

我和我的同事似乎找不到设计中的任何错误、直接将电路板的封装尺寸与数据表第 4 页的焊球图“顶视图“进行比较:

https://www.ti.com/lit/ds/symlink/opa2328.pdf

当信号被施加(在芯片 A5 焊球旁边的去耦电容器上测量)时,芯片会在各种板上整齐地获得 3.34V +/–20mV 的电压,该电压应完全在其工作范围内。

假设我不是第一个使用 DSBGA24 封装到 OPA2328 的人,我认为在生产中出现了问题。

我们还将进行 X 射线检查、但这需要一些时间、所以我想问是否存在任何可能导致内部压力的已知生产风险?

例如、此封装是否对由于焊盘中过孔回流而可能使用的高或长回流峰值特别敏感?

我很快就认为它可能是偶然的 OPA3S328、但芯片上的印刷版似乎是 OPA2328。 如果是 OPA3S328 来解释它、因为这样:

余弦进入“+IN B“

正弦进入“-IN B“

放大器 B 的输出从“OUT B“变为余弦通道的输出、并进入“+IN A“

然后、“OUT A“就像预期的那样通过“-INA"路“路由、使该输出成为一个电压、然后是另一个输出信号

这与余弦输入的相位不完全匹配、但在第一看来、它在示波器上看起来像这样、两个输出在正弦/余弦截距上从 V+到 V-会很硬摆动

但随后、一批 OPA2328 实际上已经被误码了。 “你听我说。“ (尽管我强烈推荐 3S328 引脚排列、因为与奇怪的 OPA2328 引脚排列相比,布线更为简单)。

等待 XRF 扫描时、我们欢迎您的任何想法。