工具/软件:

尊敬的专家:

您能帮助我们解决这个模型问题吗?

e2e.ti.com/.../TLV7011_5F00_sim2.TSC

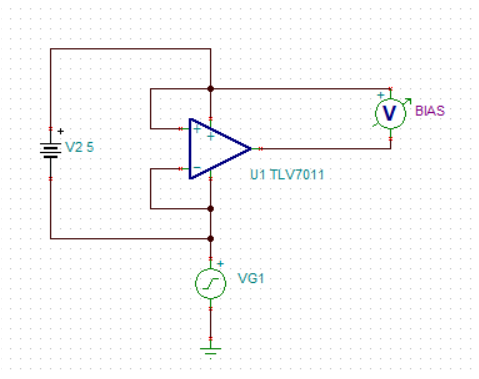

如您所见、TLV7011 的电源固定为 5V、通过将输入 IN+和 IN-分别连接到 Vcc 和 Vee、不会超出共模(虽然这是比较器,但 CM 可能不是问题)。

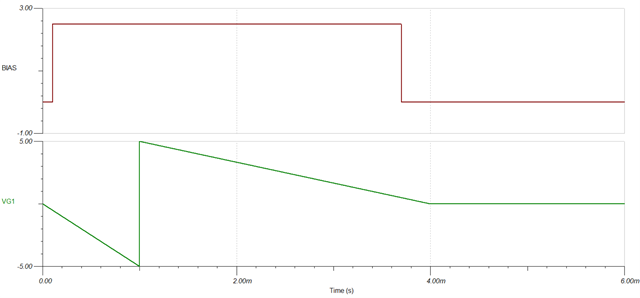

无论 VG1 电源如何变化[(0 到–5V @ 1ms)、然后(–5V 到 5V @1ms)...在上述设置下、输出应始终等于 Vcc。

因此、应预期电压表(偏置)始终等于零(因为 Vout 应等于 Vcc)。

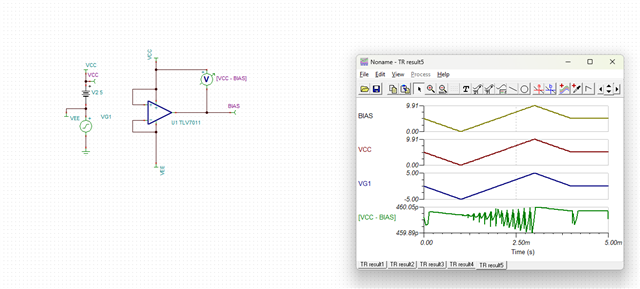

但结果却不同:

您能支持这个问题吗?

此致、

阿奇·A·

PS: 此应用用作 PMOS 1.8V 电源轨开关的栅极驱动器。 比较器的负电源轨 (V-) 由电荷泵逆变器驱动、以便为 MOSFET 提供足够的栅极驱动。