Other Parts Discussed in Thread: TPA3129D2EVM

工具/软件:

大家好、我对所有这些都很陌生。

我将通篇引用 TI 数据表。

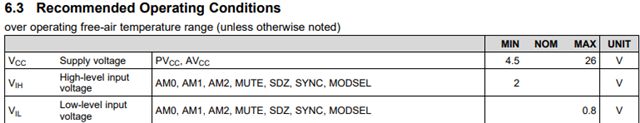

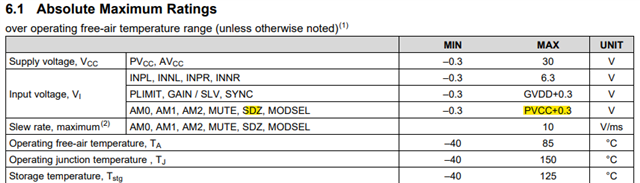

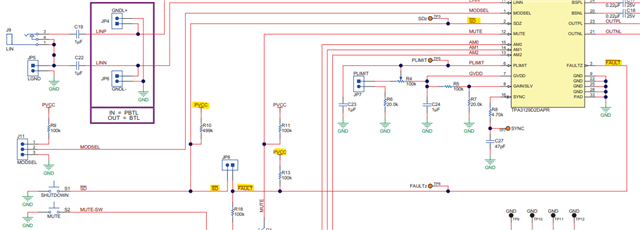

我的困惑源于引脚说明的措辞。 对于 SDZ 引脚和其他逻辑引脚、其读数为“符合 AVCC 的 TTL 逻辑电平“。 对我来说、这意味着我应该用 AVCC 上拉引脚。 我的第一个问题是、如何连接这 2 个 LED? 只是从 AVCC 引脚上连接吗?

我的第二个问题关于第 7.3.10 部分“短路保护和自动恢复“功能、该功能说我可以通过直接连接 SDZ 和 FAULTZ 来实现自动恢复。 我的问题是这种联系应该在哪里? 我同样可以通过 AVCC 上拉 FAULTZ 吗?

最后、我对图 36 感到困惑。 第 8.2 部分典型应用。 此处 SDZ 引脚被 GVDD 上拉。 这让我感到困惑、尽管图 28 中 GVDD 也上拉了 SDZ、FAULTZ 和 MUTE 引脚。 第 7.3.10 节. 让我感到困惑的原因是、在 GVDD 的引脚说明中指出、“不要用作电源或连接到 1μF X7R 陶瓷去耦电容器以及 PLIMIT 和 GAIN/SLV 电阻分压器以外的任何元件。“ 我想知道为什么在数据表原理图中这样使用它。 如果我无法使用 GVDD、如何将 AVCC 连接到逻辑引脚以将其上拉至高电平?

奖励问题! 如果我不打算添加静音功能、我是否可以将 MUTE 接地?

感谢您阅读所有这些内容。