Other Parts Discussed in Thread: OPA694

尊敬的各位:

我是Andrea Celentano,在高能量物理学领域工作的"国家科学研究所"的工作人员科学家。

我们正在使用OPA694为粒子物理探测器设计快速放大器。 过去,我们在其他电路中使用了此部件,结果非常好。

我有一个关于PCB设计细节的问题,特别是OPA 694不同信号轨迹的布线。

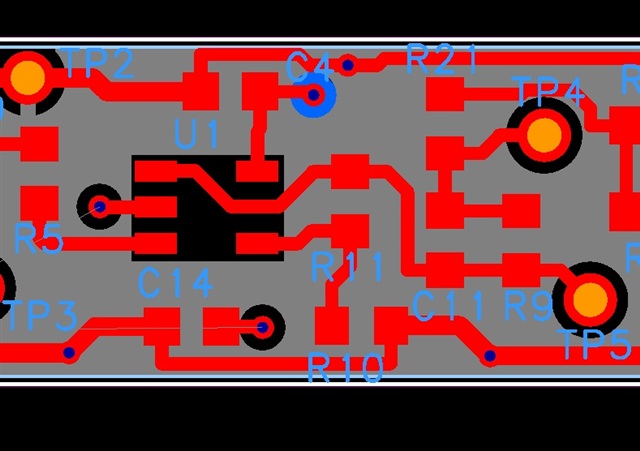

在下图中,您可以看到我们正在设计的PCB的视图。 这是一个4层电路。

灰色平面为GND。 红色的迹线位于上基准面上。 6个垫是将要安装的OPA694 (我们使用SOT23-5 6引脚DRB封装)。 左上角的引脚是1号引脚输出。

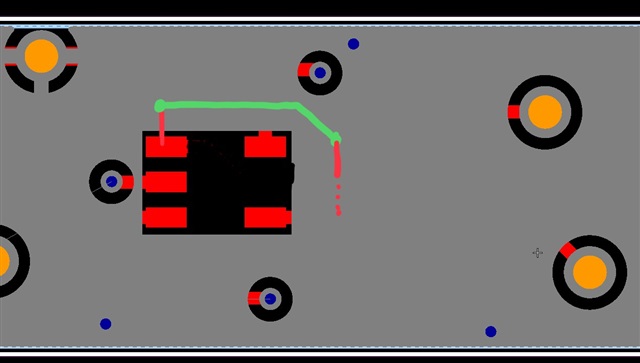

如您所见,GND平面被切割到OPA 694周围。 但是,我们在顶层有一条路由的跟踪,就在OPA694的正下方(出于设计原因,无法以不同的方式在顶层路由此跟踪)。

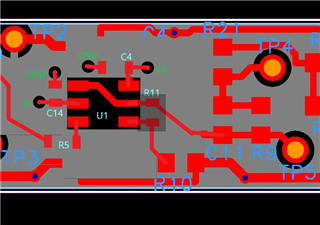

另一种方法是在内部图层中路由此迹线,方法是添加两个导通孔,如下图所示,其中绿色迹线位于中间图层。 在这种替代方法中,输出信号跟踪不会在OPA694下运行,但有两个通量成瘾。

请问您的首选配置是什么?或者这些配置是否基本相同?

谢谢!

Andrea