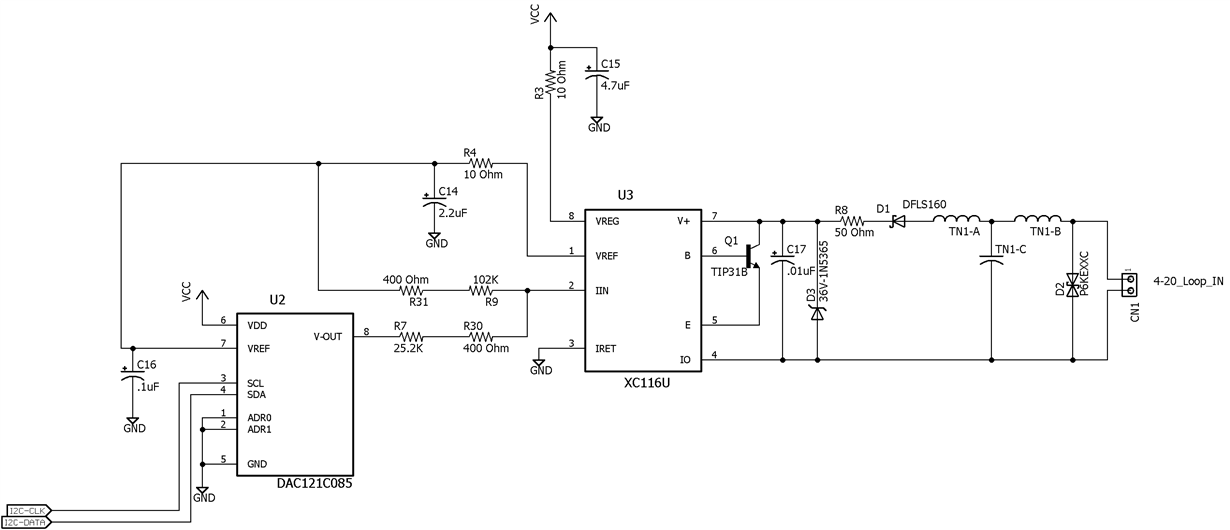

上面的示意图显示了我们希望的设计的相关部分。 对设计的一些评论:

1.它是一种环路供电设备,带有驱动DAC的PIC 18F ucontroller。 来自Vreg输出的总电流消耗约为1.5 mA。

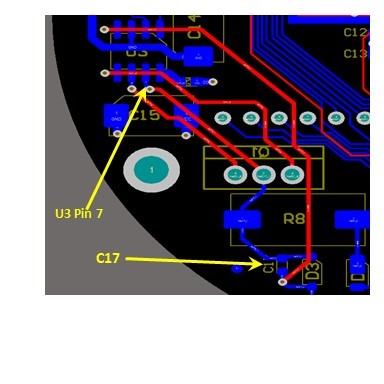

2. XTR116的Vref如上所示进行连接,而不会出现其它情况。 线路上电容的补偿如上所示,除了杂散电容之外,线路上没有额外的电容。 主板布局在DAC和XTR116周围和之间的区域非常紧凑。

3. Vreg线路驱动原理图上所示的4.7uF电容和另一个1.5uF分布式去耦电容器。 此外,PIC有一个内部调节器,在这种设计中处于活动状态,需要一个连接到PIC的外部10uF盖。

4. 4-20 mA输入上的"T"滤波器是TDK的现成EMI滤波器,部件号ACH32C-333-T

我们的问题如下:

1.在为4-20 mA回路供电时(实验室电源设置为18 VDC,安培表串联,但无其它),Vreg输出将转至大约1.5 VDC并保持在该处。 Vreg和Vref输出似乎都处于电流限制中,4-20 mA回路电流达到28至29 mA。 这很容易重复,即使PIC的复位保持激活(PIC复位)也会发生。

2.如果电源快速循环(从开到关再到开),Vreg和Vref输出将达到其正确的级别,并且所有功能都按预期工作。

3.如果关闭电源几秒钟,问题会再次出现。

我们的想法是增加R3的价值,但在初始设计阶段没有找到有关此问题的具体指导。 我们处于调试阶段的早期阶段,但希望我们能够提供任何信息。

提前感谢!

Joaquin