主题中讨论的其他器件: TINA-TI

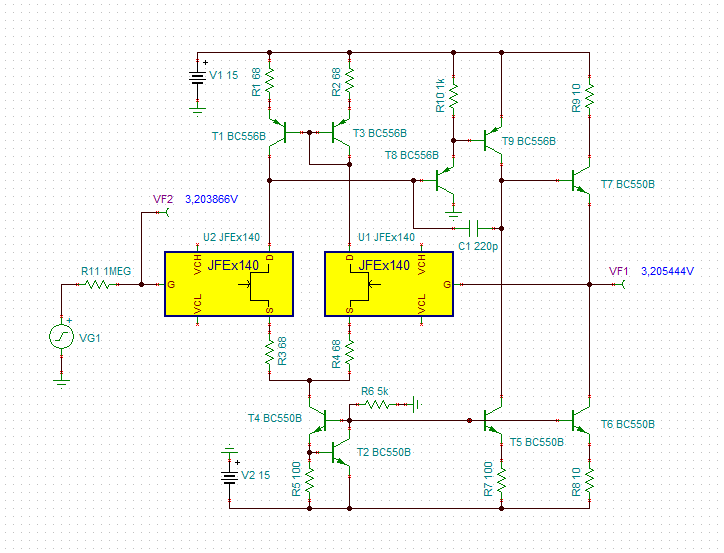

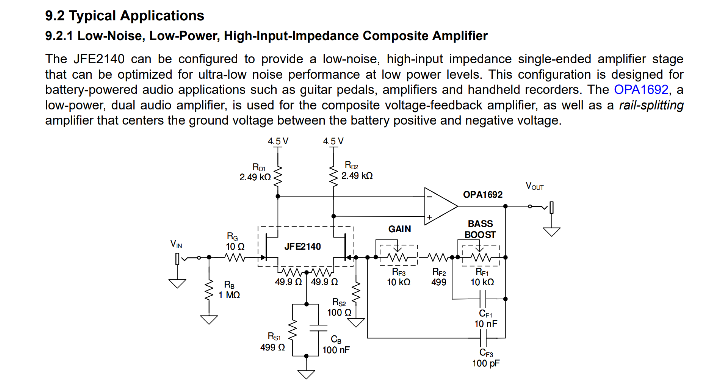

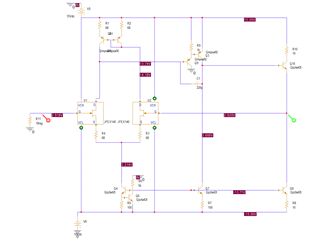

我正在研发用于音频目的的分立式运算放大器、JFE2140似乎非常适合用作输入级。 但是、在将模型导入到我的首选仿真 Microcap 12中时、我看到输入偏移量偏高。

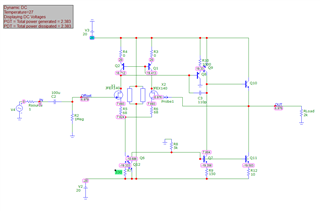

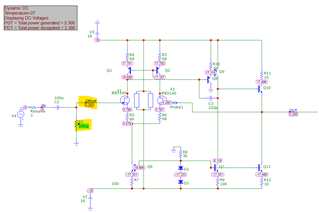

我能够在 PSpice for TI 中大致复制此行为

因此、我不认为它反映了导入或仿真软件中的错误。

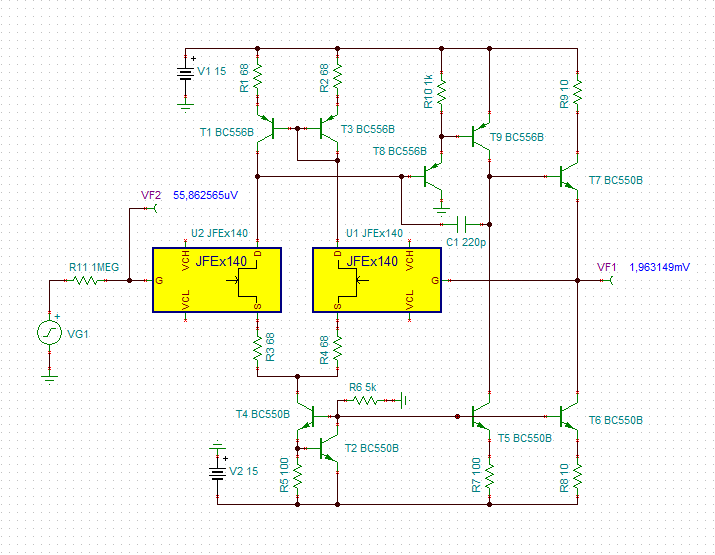

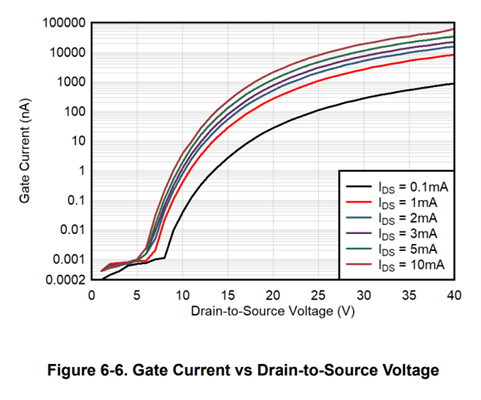

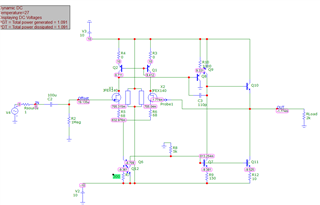

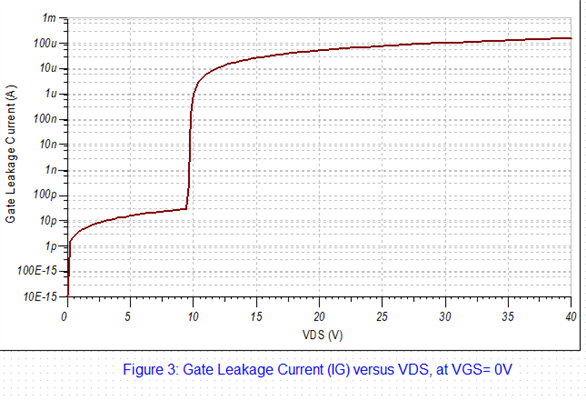

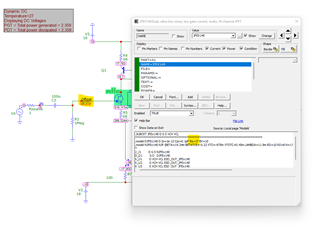

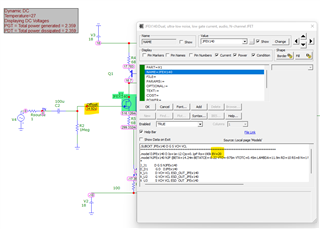

更改集成二极管 Rs

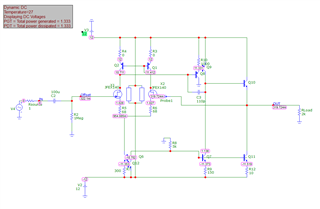

和击穿电压

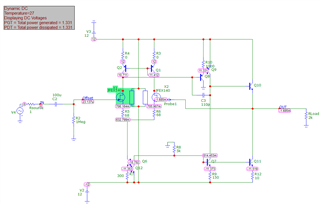

这两个值似乎都恢复了数据表中的正确行为-是否可以检查当前.lib 中的值是否正确?

我要注意的是、即使在二极管浮动的情况下、此修复也有效、在我的测试中、二极管悬空似乎不会影响 SPICE 中的失调电压行为。