您好!

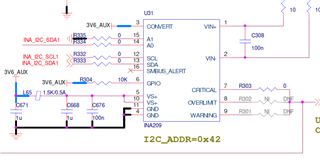

我在我的设计中使用10 x INA209。

f= 100KHz

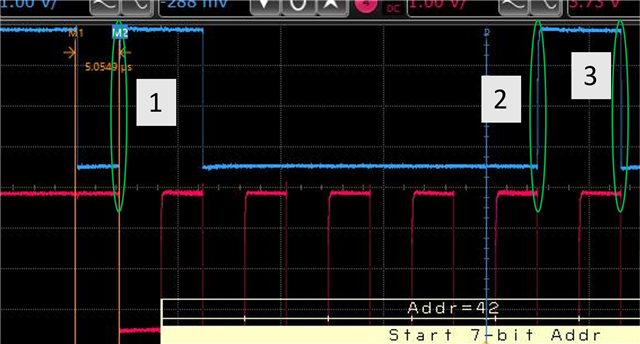

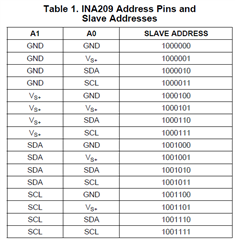

我无法访问通过 strappin A1 A0到 SDA/SCL 配置为 I2C ADDR 的地址(例如、L addr 0x42 (a1=GND、A0=SDA))

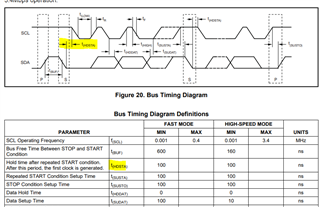

DS 表示:

'引脚 A0和 A1的状态需要一个寄存器指针的值。

在每次总线通信时被采样并且应该写入一个寄存器以第一个字节开始

在接口上发生任何活动之前进行设置"

您能不能详细说明 A1 A0被采样的时间点

为了正确捕捉地址、SCL/SDA 是否有任何时序限制?

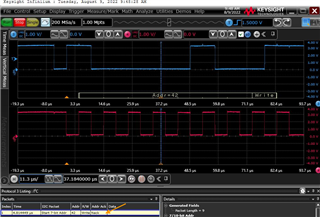

添加用于访问0x42的图片-无确认

添加了用于访问0x44的图片-使用 Ack

谢谢

Dror