Other Parts Discussed in Thread: LMH6401, SN74CBTLV3251

主题中讨论的其他器件: SN74CBTLV3251

您好!

我想通过同一 SPI 总线以菊花链形式连接64个车床部件、直接将 SCLK 和 SDI 引脚与单独的独立 CS 和 SDO 连接在一起。 有可能吗? 您能告诉我 SCLK 和 SDI 所需的电流吗?

谢谢。

虚拟磁盘

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Other Parts Discussed in Thread: LMH6401, SN74CBTLV3251

您好!

我想通过同一 SPI 总线以菊花链形式连接64个车床部件、直接将 SCLK 和 SDI 引脚与单独的独立 CS 和 SDO 连接在一起。 有可能吗? 您能告诉我 SCLK 和 SDI 所需的电流吗?

谢谢。

虚拟磁盘

尊敬的 VD:

我将与我的团队核实此设计的可行性。 将来、您可以编辑帖子以添加其他问题、或使用"提出相关问题"按钮、而不是发布两个单独的问题:

我将在本活动主题中回答您的全部问题。

最棒的

阿尔茨

您好、Vigus、

我认为菊花链的容性负载是这里的真正问题。 请记住、与 I2C 总线相反、SPI 是一种运行频率高达50MHz 的高速总线。 这需要主器件中的 SCLK 驱动器提供陡峭的边沿。 当主器件仅连接两三个 LMH6401且 SCLK 线的距离仅为几厘米时、这种方法效果会很好。 但是、当驱动更长的菊花链传输线路时、会看到回音和振铃等效应。

对于点对点传输(一个主器件和一个从器件)而言、较长的传输线路不是问题、因为您可以在驱动器上轻松引入串联端接。 但是、当以菊花链形式连接多个从器件的多个输入电容时、这些从器件将发挥作用。 即使不使用串联端接、这也不起作用。

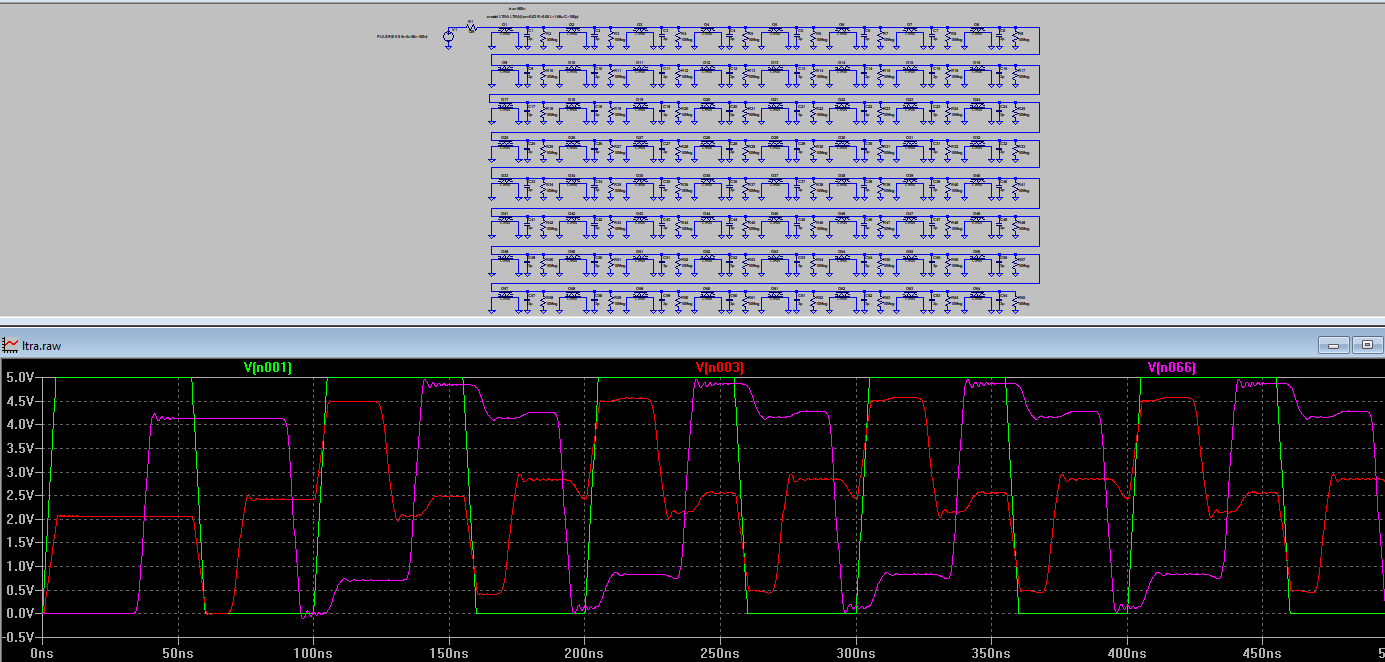

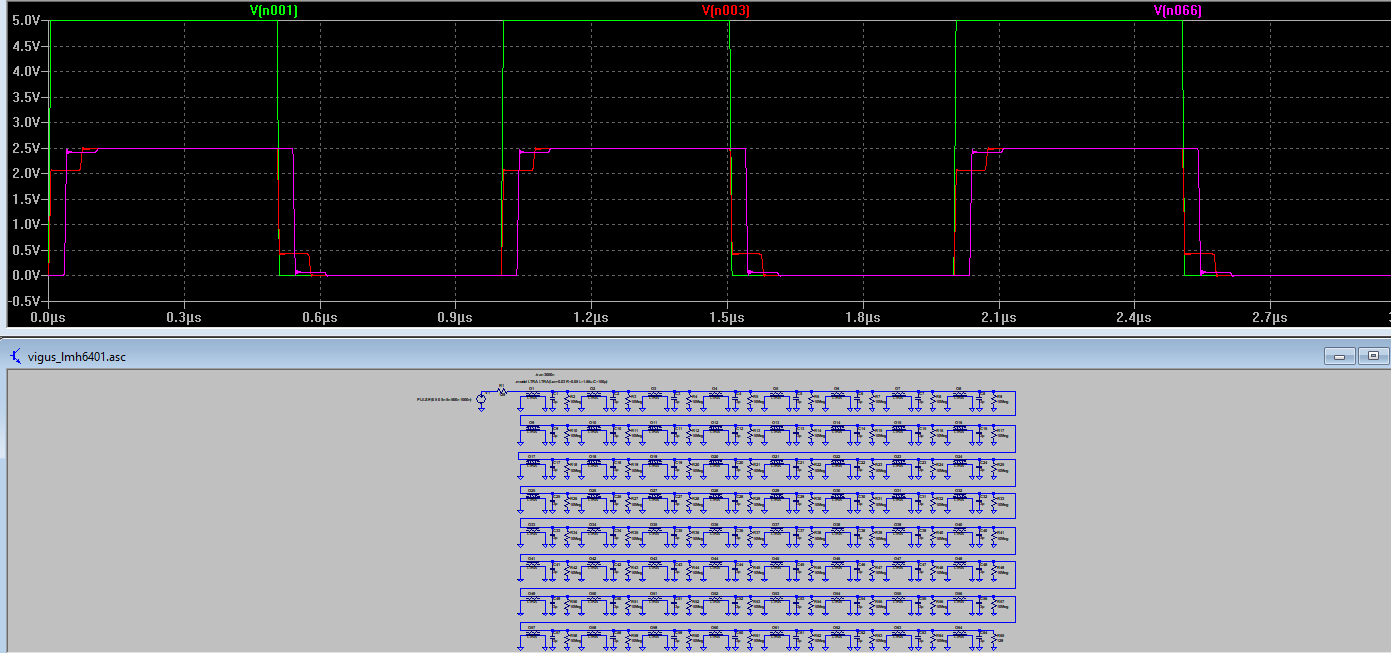

在以下仿真中、您可以看到包含64个从器件的菊花链的行为、每个从器件都具有3pF 输入电容、所有从器件的距离均为3cm 长0.3mm 宽铜轨、并通过140µm Ω 长的实心接地层进行布线。 3cm 长的铜轨相当于约129欧姆的传输线路阻抗、整个菊花链通过主器件上的129R 电阻器进行串联端接:

绿色曲线是上升和下降时间为5ns 的主器件的10MHz SCLK 信号。 红色曲线是第一个从器件接收到的信号、紫色曲线是最后一个主器件接收到的信号。 您可以清楚地看到、回声完全破坏了 SCLK 信号。

将主器件信号的上升和下降时间增加至100...200ns 并将时钟速率降低至1MHz 以下有助于避免令人厌烦的回声。 但从器件必须能够在其输入端接受减少的上升和下降时间。

e2e.ti.com/.../vigus_5F00_lmh6401.zip

Kai

您好、Marvin、

首先、需要了解 SPI 总线的实际物理外观。 实际距离是多少? 总线是如何拆分的? 因此、布局非常有用。

由于传输线路的信号延迟不可避免、总线线路从主器件到任何从器件的最大距离决定了最大时钟速率。

然后、可以尝试在两端端端端端端接传输线路(总线线路)。 这将允许许多从器件连接到同一传输线路、从而比点对点传输更多的从器件。 但是、由于信号抑制、最终需要在输入和输出端使用特殊的总线线路驱动器/接收器:

Kai

尊敬的 Alec 和 Kai:

布局尚未完成、但我附上了示例布局和客户提供的更多信息

您好、Marvin、

在子板上插入施密特触发接收器时、您可能会成功。 每行一个。 这会将总线与每个子板上的四个 LMH6401的容性负载隔离。

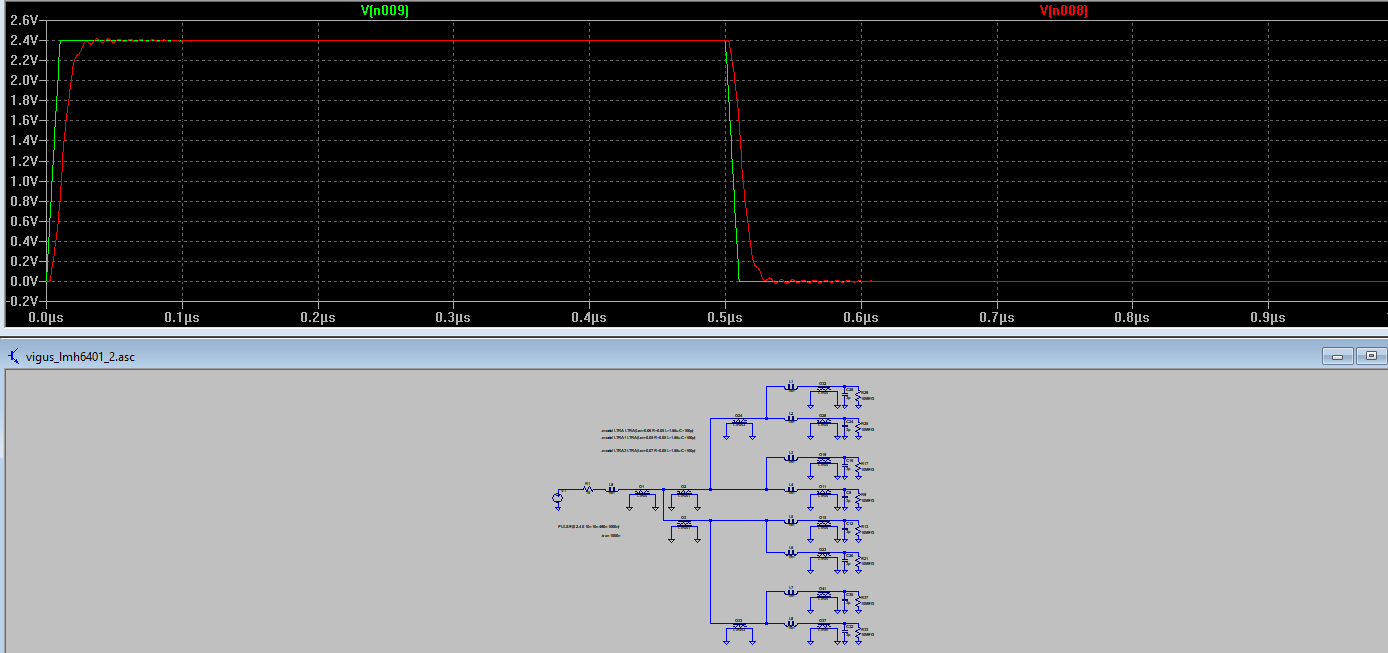

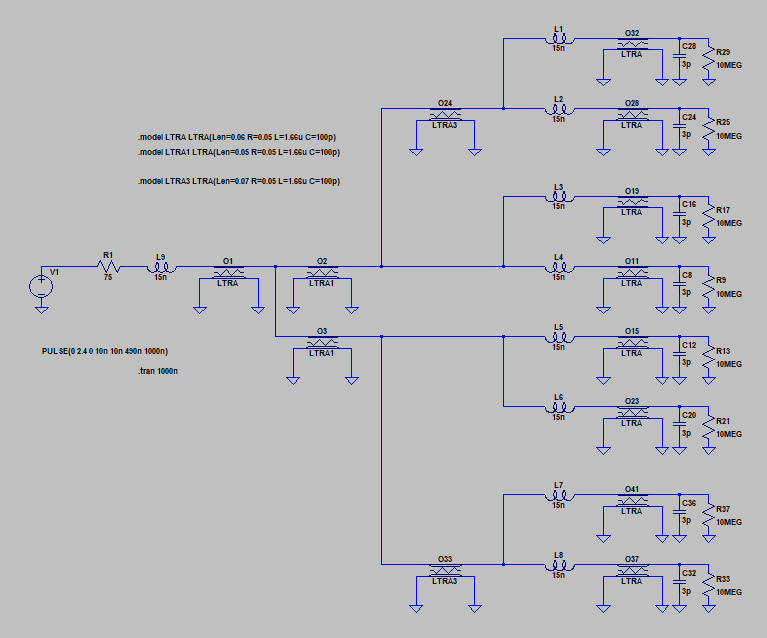

以下仿真显示了电路板上129R 传输线(在140µm Ω 距离实心接地层上布线的0.3mm 宽铜轨)、1MHz 的2.4Vpp 方波(上升和下降时间为10ns)以及简单的75R 系列端接的情况。 总线线路由不同长的传输线路和由15nH 电感模拟的连接器:

e2e.ti.com/.../vigus_5F00_lmh6401_5F00_2.zip

通过使串联端接电阻小于传输线路阻抗、可以生成无纹波的边沿。 当然、您必须对串联端接电阻器的具体值进行实验、以优化结果。

为了实现稳定的性能、必须满足某些要求:

1.您不能将总线线路彼此靠近。 串扰将完全破坏信号完整性。 您必须通过总线线路之间足够宽的接地填充来隔离总线线路、您必须将总线线路连接到底层实心接地层、尽可能多的过孔(至少每10mm 左右)。

2.此外,您必须将总线线路布置在实心接地层上。 只有遵循这两条设计规则、才能防止串扰、并实现可预测的信号形状。

3.为了远离舍入拐点和来自施密特触发接收器阈值电平的信号纹波、方波放大不应超过施密特触发接收器阈值电平的两倍。

4.用没有太陡边的方波驱动总线线路很重要。 因此、此处的总线线路驱动器快照不会太快。 越慢越好。 运行仿真以查看上升和下降时间对不需要的振铃的影响。 它主要取决于施密特触发接收器可以接受多少振铃。

5. SPI 总线的时钟速率不应太快。 我建议保持低于1MHz 左右。

最后一个提示:请记住、在总线线路之间使用接地填充将改变传输线路阻抗。 在运行仿真时应考虑这一点。 在上面的仿真中、我没有假定这些接地填充。

Kai