Other Parts Discussed in Thread: AFE032

大家好、

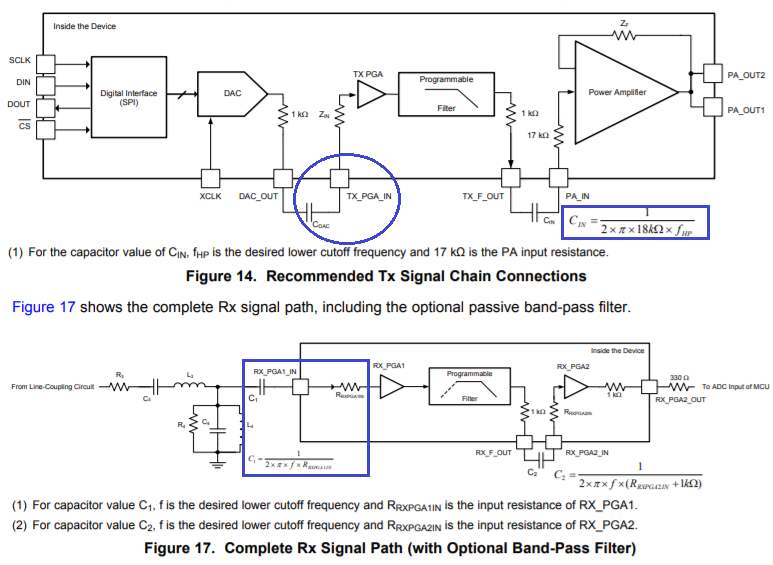

我的客户正在开发 AFE032。 由于内部 DAC 的位数无法满足客户的要求、因此客户使用外部 DAC 并将 DAC 输出馈入内部 PGA。

为了验证 AFE032自身的性能、客户将 DAC 输出断开至内部 PGA 并将 TX_PGA_IN 引脚悬空。 然后、客户按照以下计划执行 AFE032:

加电初始化阶段:步骤1~8

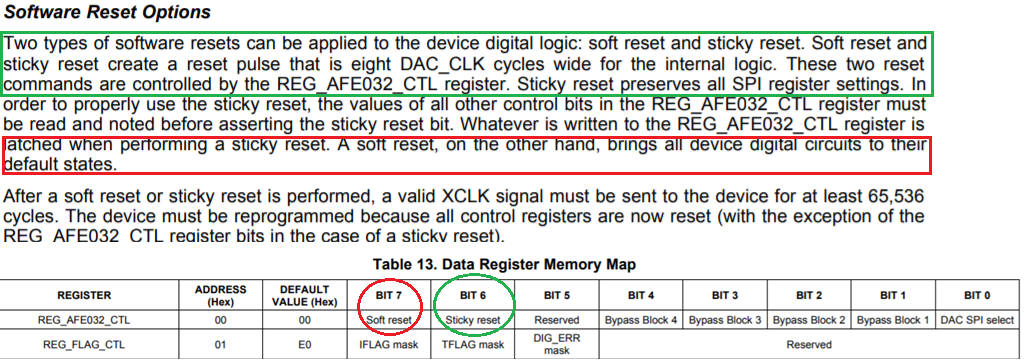

reg00->0x80; //位7→1:软复位

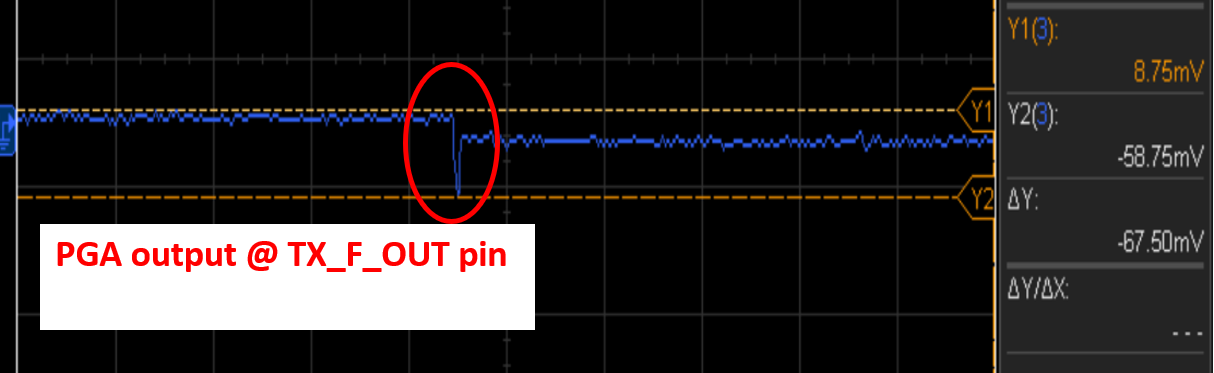

在这句话运行后、我们发现 PGA 输出会生成杂散

delayclk (66000拍)

reg08->0x1C; //位4→1:PA_NRF 使能,//位3→1:TX_RX_NRF 使能,//位2→1:DAC_NRF 使能

4.reg0F->0x11; //位4→1:clk 分频 器//位0→1:clk 分频器

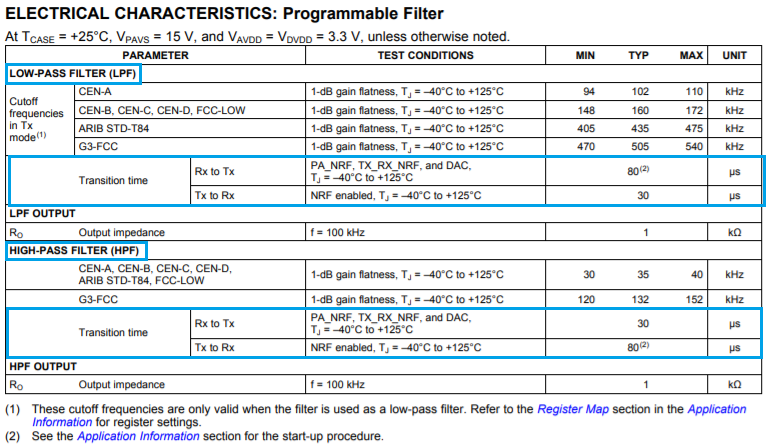

5.reg05->0x30; //位[6:4]→011:LPF=490kHz。

6.reg05->0xB0; //设置启用辅助位

7.Reg06->0x02 //位[2:0]→010:TX_PGA 增益=3.25。

8.Reg03->0xE0 //位7→1:LPF 被启用 //位6→1:HPF 被启用 //位5→1:滤波器偏置被启用

PA 使能 序列:步骤1~10

1.Reg04->8'hB0; // Bits [7:6]→10:Set PA Iq =95mA。// Bits [5:4]→11:Set PA Current Limit=3.0A

reg03->8'hB0; //位7→1:LPF 使能//位6→0:HPF 禁用//位5→1:滤波器偏置使能//位4→1:PA 使能

3.Reg06->8'h10; //位4→1:TX_PGA 启用, //bit3→0: RX 禁用(默认) //位[2:0]→000:TX_PGA 增益=1.15

在这句话运行后、我们发现 PGA 输出会生成杂散

4.Delayus (53)

5.Reg03->8'hB4; //位7→1:LPF 启用//位6→0:HPF 禁用//位5→1:滤波器偏置启用//位4→1:PA 启用//位3→0:PA 输出级禁用

//位2→1:DAC 使能

6.Delayus (21.7)

:REG03->8'HBC;//位3→1 μ s 启用 PA 输出级

8.Reg04->8'hBC://位2→1:ENPAIQP //位3→1:ENPAIQN

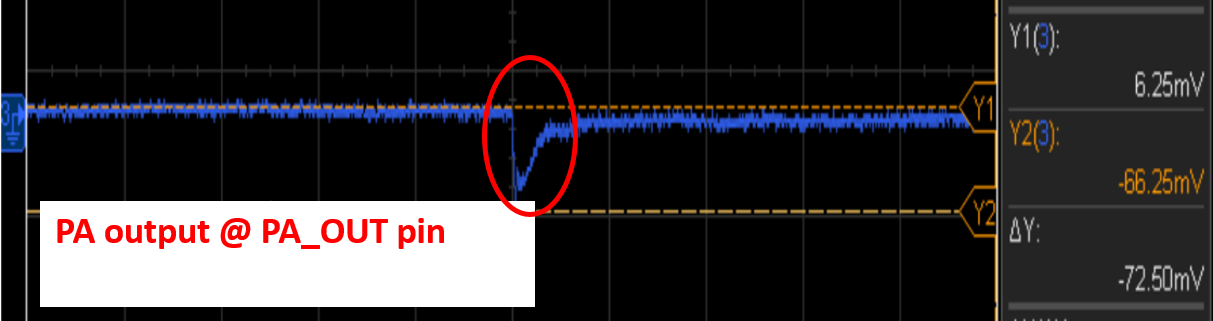

在这句话被操作后、我们发现 PA 输出会生成一个杂散

9.Reg06->8'hd0; //位7→1:ENPCOMP //位6→1:ENNCOMP

10.Reg06->8'HD2 //位[2:0]→010:TX_PGA 增益=3.25

因此、根据我们的测试:

在 上电初始化阶段 、在第1步操作后、我们发现 PGA 输出会生成杂散

在 PA 使能 序列 中、在操作步骤3后、我们发现 PGA 输出会生成杂散。 在第8步运行后 、我们发现 PA 输出会生成杂散。

那么、您能否帮助评估这种现象是否正常? 它与硬件或寄存器序列相关吗? 谢谢。

此致、

韦恩