Other Parts Discussed in Thread: INA114

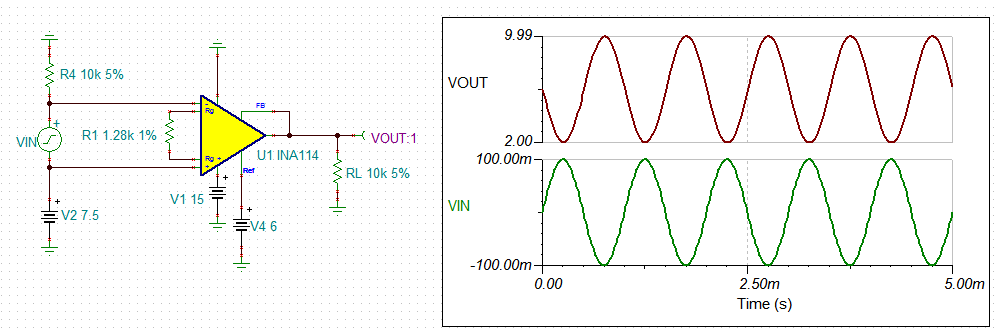

我在具有单个+15VDC 电源的惠斯通电桥电路中使用 INA114、我观察到(在示波器上以及在 TINA 中)输出波形在大约2倍于电桥的共模电压时发生削波或饱和。

例如、当我在 Vc=+4.900V 之上输入200mVpk-pk 正弦波(因此 Vd/2从0变为+100mV;从不变为负值)时、输出似乎在+9.8V 附近发生削波/饱和。 (我将增益设置为40、电压基准为+2.0V、因此输出波形应从+2V 变为+10V。) 在 TINA 中、当我将 VC 更改为+3.000V 时、它会在+6.0V 左右发生削波/饱和。

根据数据表、这种情况不应发生。 当我有一个+15V 电源时、输出摆幅应至少达到+13V、不是? (注意、我发现输出信号的低电平部分在+2V 附近没有问题... 波形的上半部分。) 为什么输出摆幅看起来跟踪共模电压(几乎恰好是双 Vc)?

此致、Matthew