您提供的分析似乎与物理测试的结果不一致。

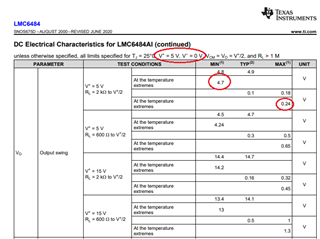

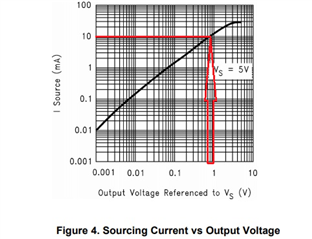

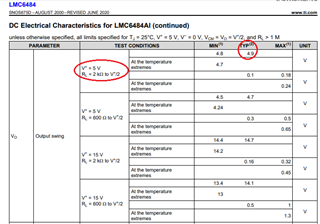

根据您的仿真 LMC6474、输出的上升时间为~5us、但鉴于 MAX1230 ADC 采集时间小于0.6us、这将导致 ADC 输出远不接近于5V -我们看到、施加5V 电压时、输出电压大约为4.7V。

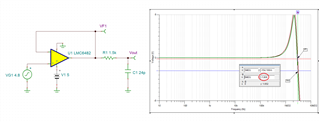

我已经在对开关施加0.6us 脉冲的情况下模拟了采样保持功能、以表示采集、并且 Vout 在此时间内达到5V。

我仍然不知道为什么我们看到 ADC 输出下降、即当我们向输入施加4.9V 直流电压时、输出大约为4.7V...

(两个仿真都产生相同的结果)