主题中讨论的其他器件: TLV3402

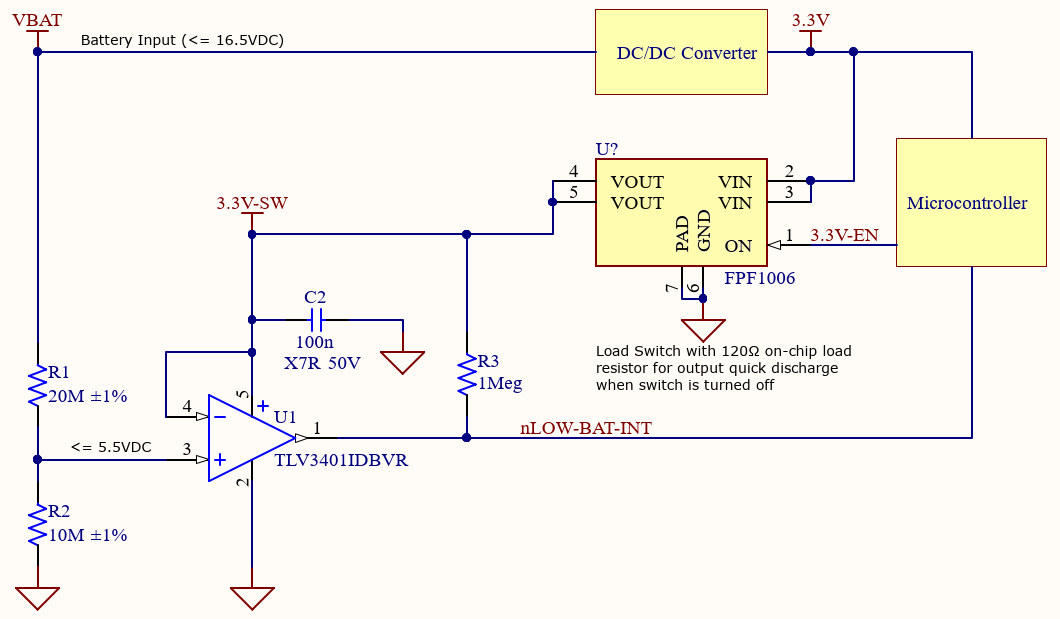

我有一个问题是、以特定的方式超过 TLV3401输入的绝对最大额定值。 下面是我们刚才制作的电路的简化版原理图。 TLV3401用于根据 VBAT 分压器(1/3分压器)检测低电池电压。 电池电压转换为3.3V、为微控制器和负载开关供电。 微控制器可以启用/禁用为比较器(和其他电路)供电的开关3.3V。 负载开关具有一个内部120欧姆放电电阻器、该电阻器在开关关闭时出现。

我们最近的情况是、我们的电池电压比最初假设的大一些。 电池电压可能达到16.5VDC、而分压器输出则可能达到5.5VDC。 如果开关断电(例如,当电池首次连接或由 uC 控制时),TLV3401的 VCC 将为0VDC,而通过20兆欧电阻将5.5V 电压施加到“+”输入。 该电压超过了“VCC + 5”的绝对最大额定值。

您能否详细介绍 TLV3401的内部结构以及在 VCC = 0时向输入引脚施加5.5V 限流的效果? 是否存在损坏、可靠性降低等风险? 我认为在这种情况下 ESD 二极管通常会导通、由于电流受限、因此可能可以。 不过、我看到这篇针对 TLV3402 https://e2e.ti.com/support/amplifiers/f/14/t/209321的 e2e 文章、其中指出输入 ESD 单元被设计为保持关闭。