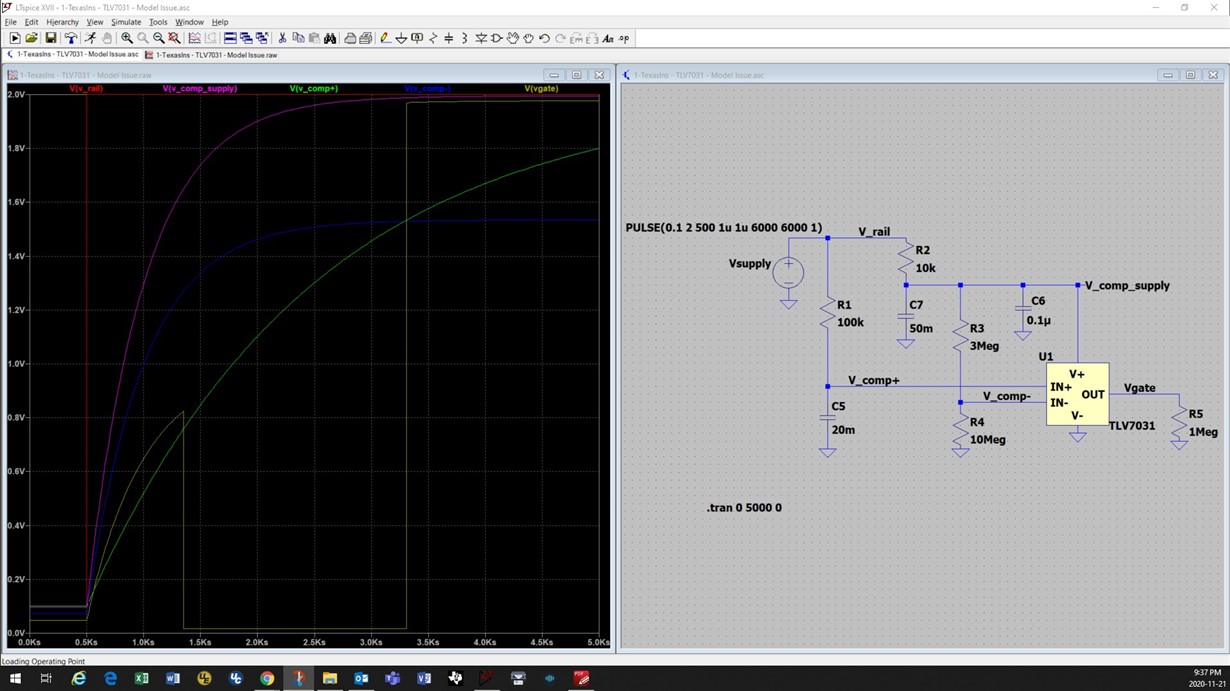

主题中讨论的其他器件: TLV7031

您好!

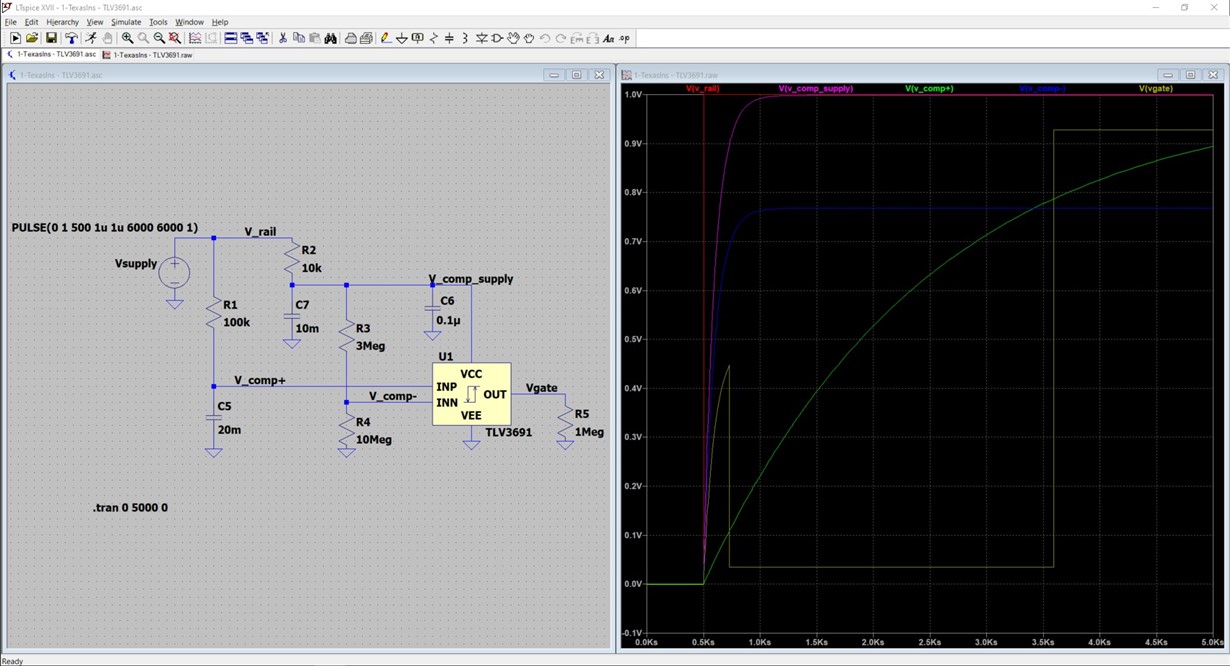

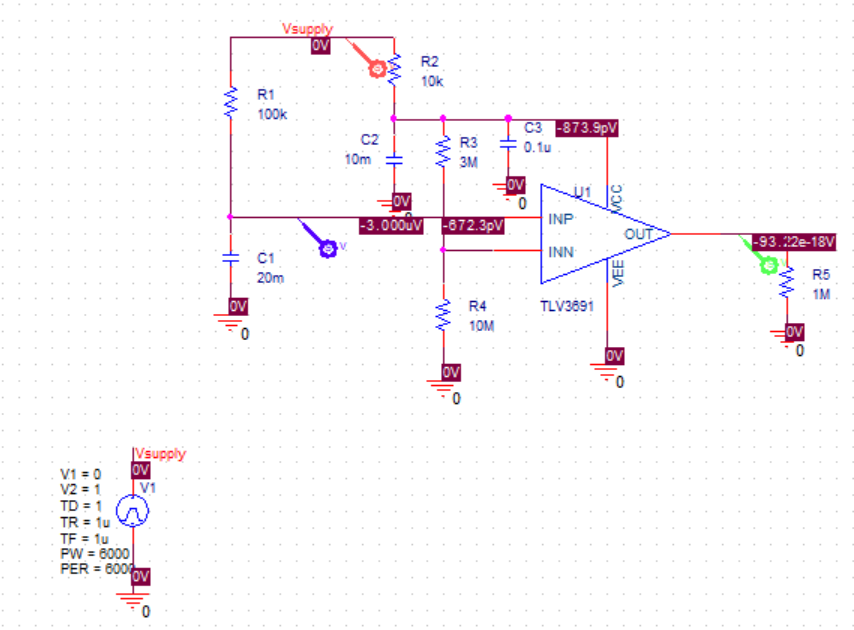

我正在研究 TLV3691在仅有一个电压源的自主电源设计中的潜在用途。 我在 LTSPICE 中仿真了比较器、如下所示。 由于 IP 问题、我没有复制过发电端。 相反、我只使用了一个电压电源来仿真一个电源。 较小的电容器 C7应存储能量来为比较器供电、较大的电容器应存储负载的能量。 TLV3691应在比较器在0.9V 电压下工作时导通 MOSFET。

我们为什么会在0.5k 和1.0k 之间的比较器输出上看到干扰? 下拉电阻器 R5是否应该确保节点"Vgate"在开关发生前保持低电平? 我在论坛上阅读了一个与我在这里讨论的内容密切相关的主题。 当比较器电源电压低于0.9V 时、规定的下拉电阻似乎无法可靠地工作。 有什么意见?

Chundra