主题中讨论的其他器件: DAC3283、 LMH5401

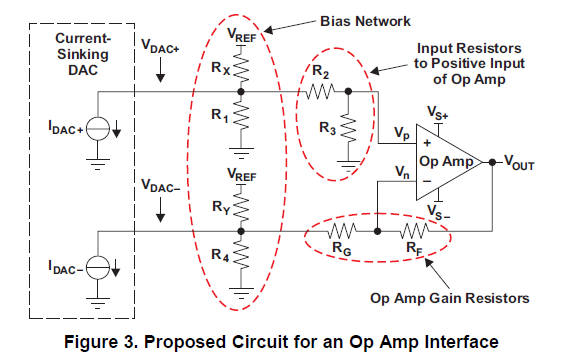

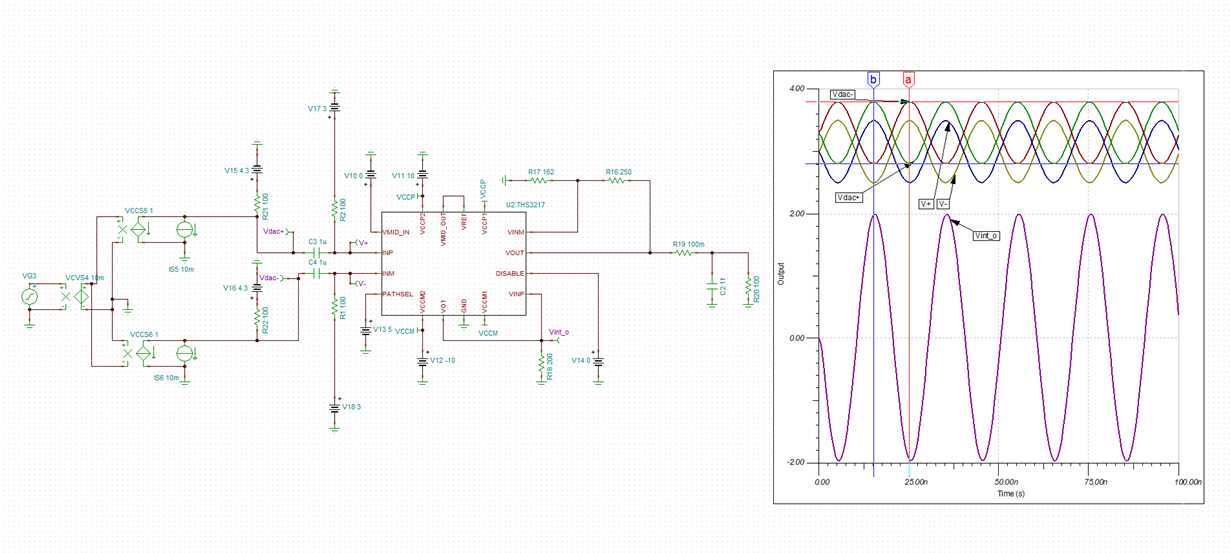

大家好、我正在使用 THS3217为灌电流 DAC3283设计接口电路。 我阅读了 TI 的应用手册、并尝试根据图3中给出的拓扑来设计电路。

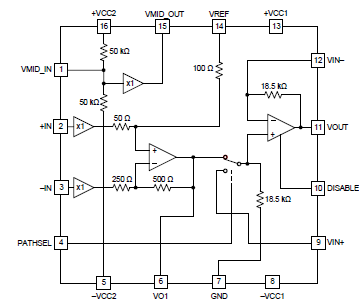

由于 THS3217为每个差分输入都有一个输入缓冲器(如引脚2/3上的 x1所示)、因此输入阻抗将非常大、因此图3中对电路的分析对于 THS3217将无效。

对吗? 如果正确、应如何设计该电路?

尽管数据表中提到 THS3217旨在简化灌电流/拉电流 DAC 之间的接口设计、但仅提供了拉电流 DAC 的设计示例。