你(们)好

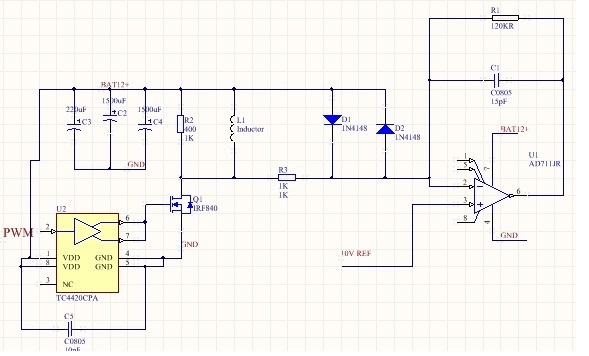

我想 让 PCB 在 schematic..in 以下放置该原理图 PWM 驱动 Q1、因此 L1从 R3汲取3A.U1 (运算放大器)反相输入馈电。

由于 L1 消耗高电流 ,我希望 将 L1 接地平面与精密 电路接 地平面分开。

但我的问题是:如何 通过接地平面间隙将 R3连接到 U1 (运算放大器引脚2)? 在整个 PCB 设计中 、建议不要在接地层间隙上通过布线 !! 另一方面 ,建议使用分区 接 地平面 来实现抗噪性能。

我绘制了一个布局并放在这里 作为示例。

在此 PCB 布局中、我使用 桥接器连接牵引 GND 平面 、并通过该桥接器将 R3连接到 U1。

这种方式 是正确的???

谢谢。

此致。