尊敬的 TI 社区:

我知道去耦线程被解释了上千次、应该遵循一些一般规则。

但我还有一些其他可能也很重要的问题。

因此、我将尝试解释我的设计以及我真正关心这些设计的原因。

我的设计是围绕几个运算放大器和模拟多路复用器构建的。

我将如下所示:

1个 OPA1604 (音频输入级) 3个并联的 OPA1622将直接驱动负载(耳机)、而 OPA1604周围的模拟多路复用器用于增益控制(由双极电源供电)。

这仅是一个通道。

我在超低噪声 LDO 周围构建了相当好的 PSU。

最常见的技术是将100nF 电容器尽可能靠近 IC 引脚放置(使用高电流输出的运算放大器时、通常建议放置大容量电容器以提供足够的电荷)。

我已经做过这个、每个运算放大器都有自己的大容量电容器(10uF)、然后是100nF 电容器+另一个更小的电容器、如1000pF。

我的 PCB 是4层电路板、因此我可以使用内层供电、以避免具有明显电感的薄/长电源迹线、或者我可以使用外层布线足够粗的电源迹线。

因此、PCB 可以由我妥善处理、在这里不应该成为问题。

问题是:

-我是否应该通过铁氧体试验(即使它们往往在更高的频率下工作)或电阻器(我将影响动态范围)将每个运算放大器电源彼此隔离。

或者我应该忘记它吗?

我应该包含这种隔离吗? 令人难以回答的问题是、我应该关心它的位置以及何时不需要它。

从理论上讲、这看起来很有希望、因为它将改善运算放大器 PSRR、并且还将使电源更清洁、因为不会有任何可能损坏其他运算放大器的"耦合污染"。

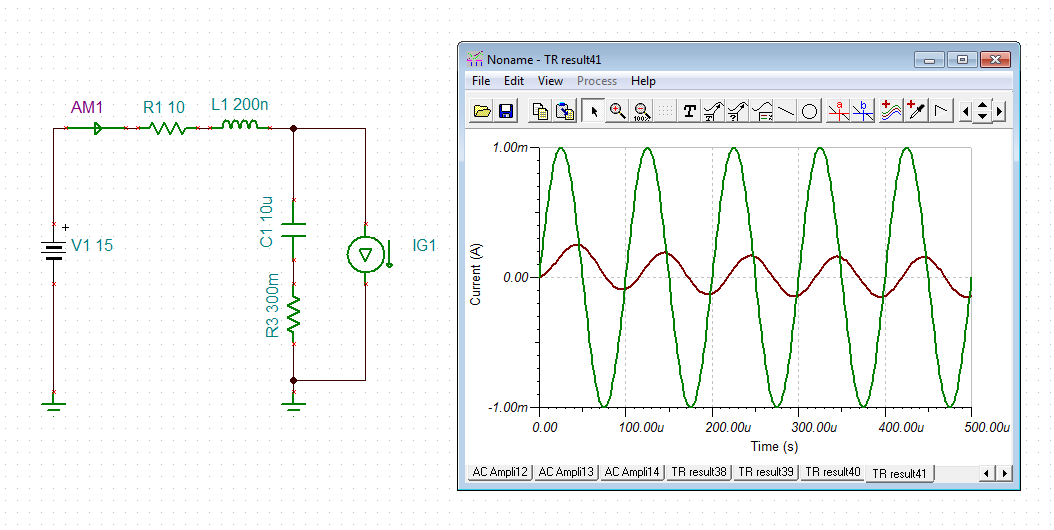

我认为这很重要、因为我的输出级是 AB 类放大器、它仅消耗一半的整流电流。

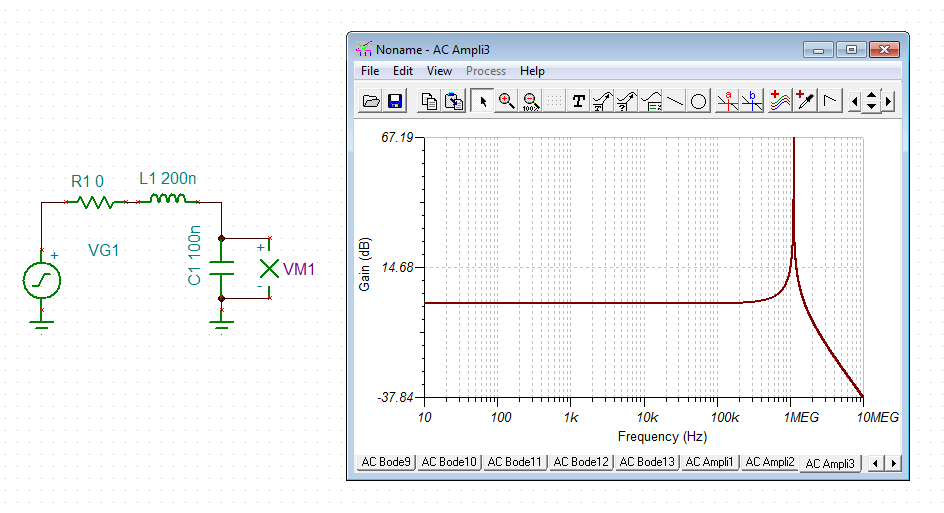

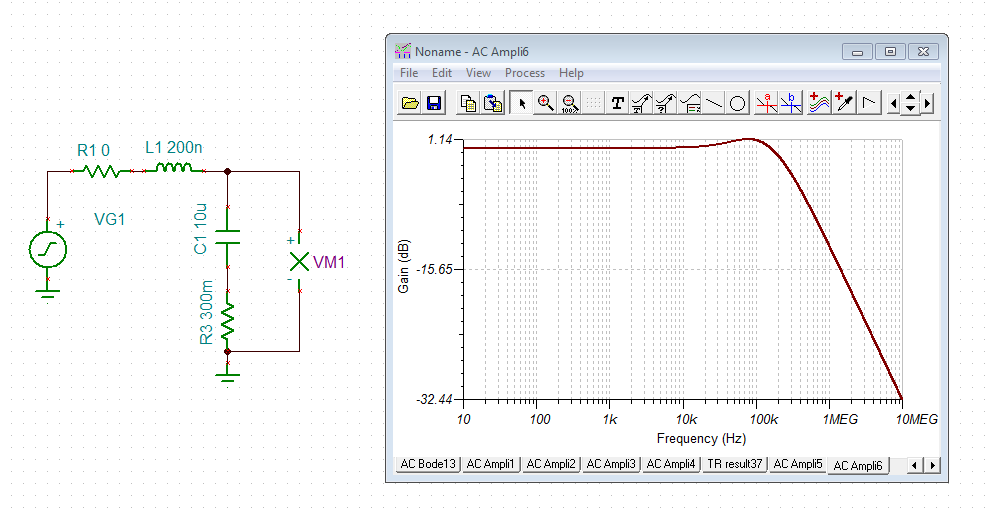

我还听说、如果连接到同一电源平面、那么为每个电源 IC 引脚放置多个小值电容器(如100nF)可能会产生谐振。

为了避免这种情况、我需要添加一些阻尼。

因此、我希望对我的帖子进行更深入的解释、因为我知道一些事情、但我认为这还不够。