主题中讨论的其他器件:TINA-TI、 OPA365

工具/软件:TINA-TI 或 Spice 模型

尊敬的所有人:

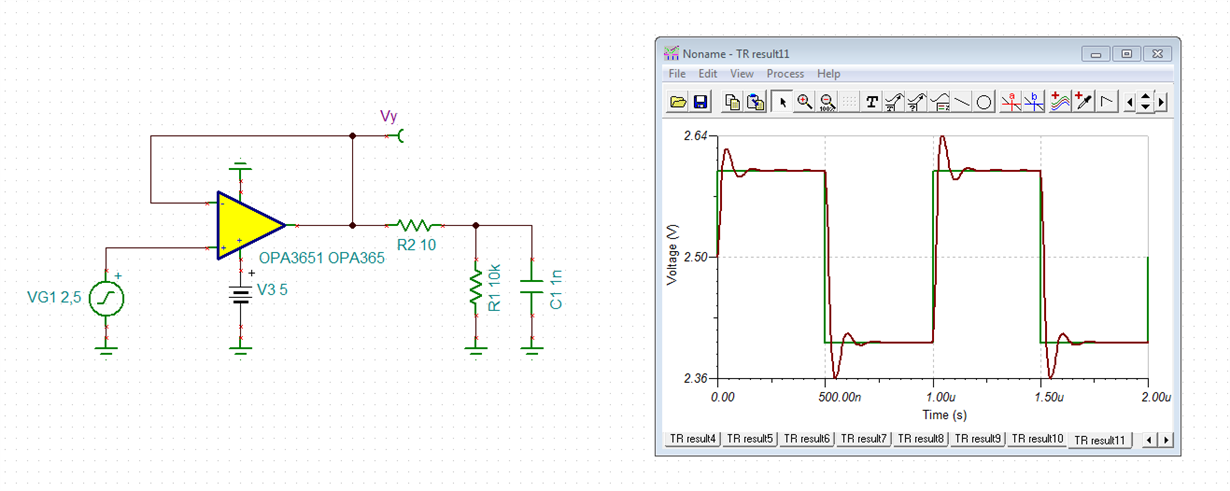

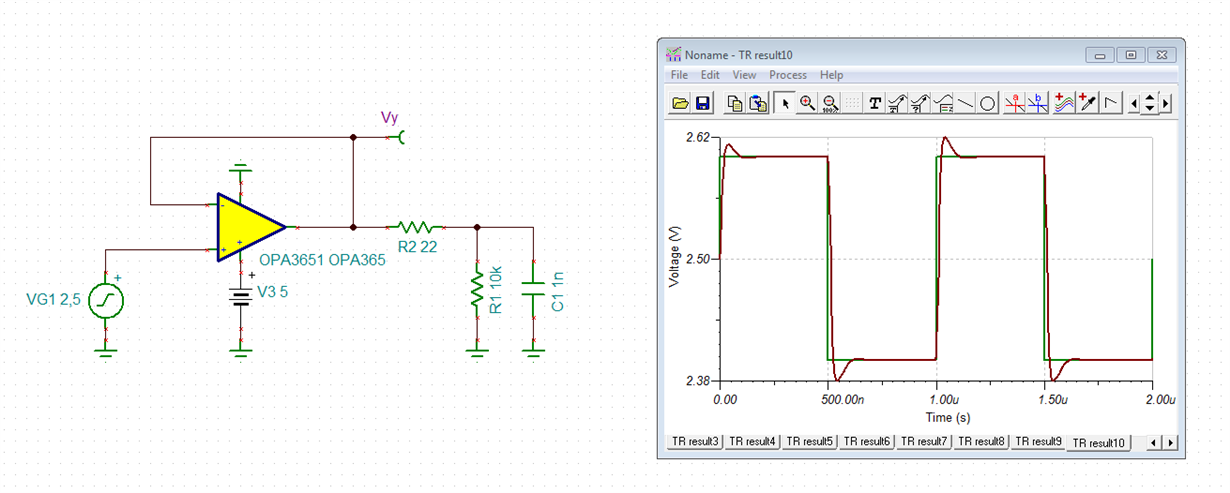

我通过 TINA-TI 仿真了 OPA365在驱动容性负载(1nF)时的相位裕度。

但相补角不是很好。 我知道我们应该有超过45度的裕度。

请检查 TINA 结果和 TINA 项目文件的以下文件。

e2e.ti.com/.../OPA365Q1-phase-margin_5F00_result.pdf

e2e.ti.com/.../OPA365Q1-phase-margin-project.TSC

您能否告诉我如何考虑相位裕度以及如何在驱动容性负载时控制相位裕度?

我在数据表中提到了"9.1.1电容负载"、因此我在输出线路上添加了串联电阻器。

现在、我计划将输入信号从 数百[kHz]更改为 数[MHz]。

此致、