Other Parts Discussed in Thread: JFE2140, OPA604, OPA202, LME49860, TINA-TI

主题中讨论的其他器件: OPA604、 OPA202、 LME49860、 TINA-TI

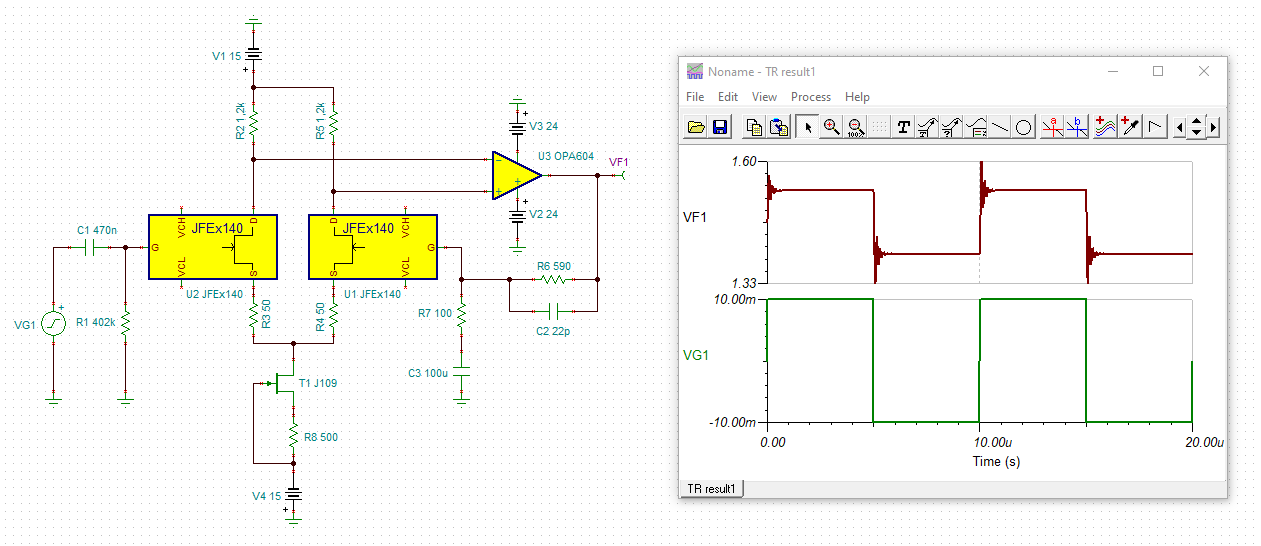

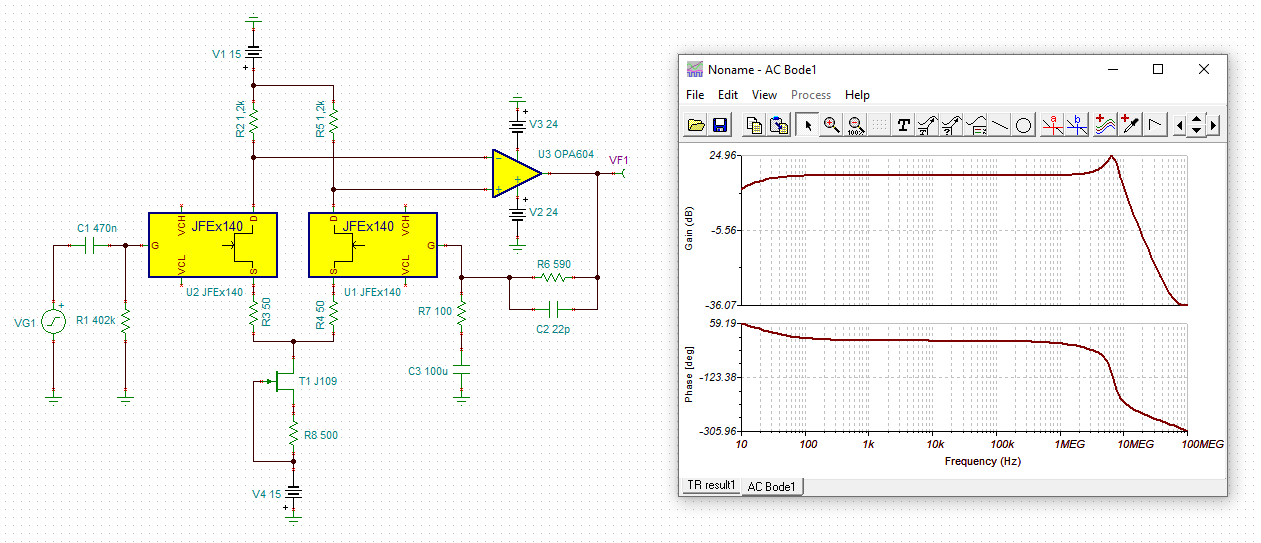

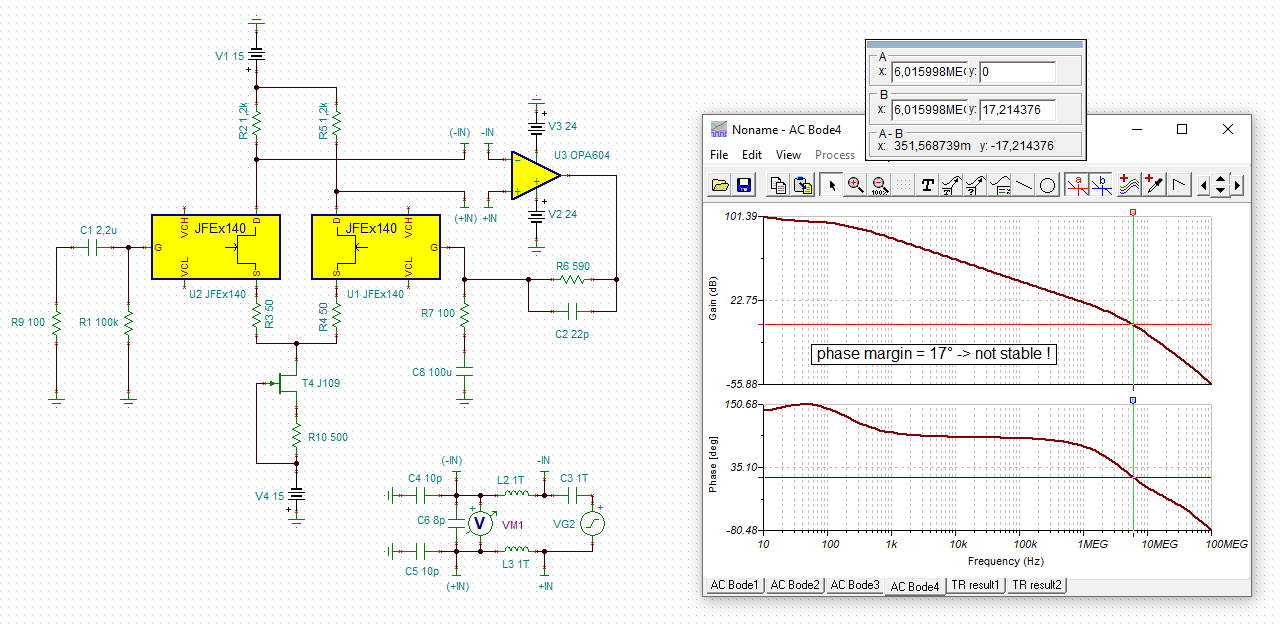

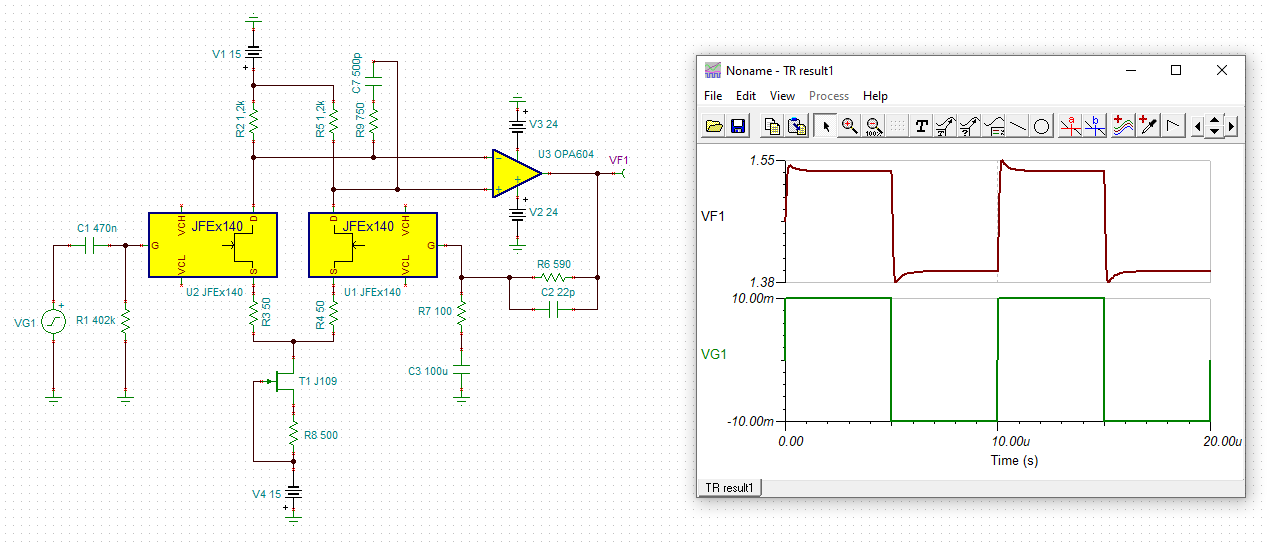

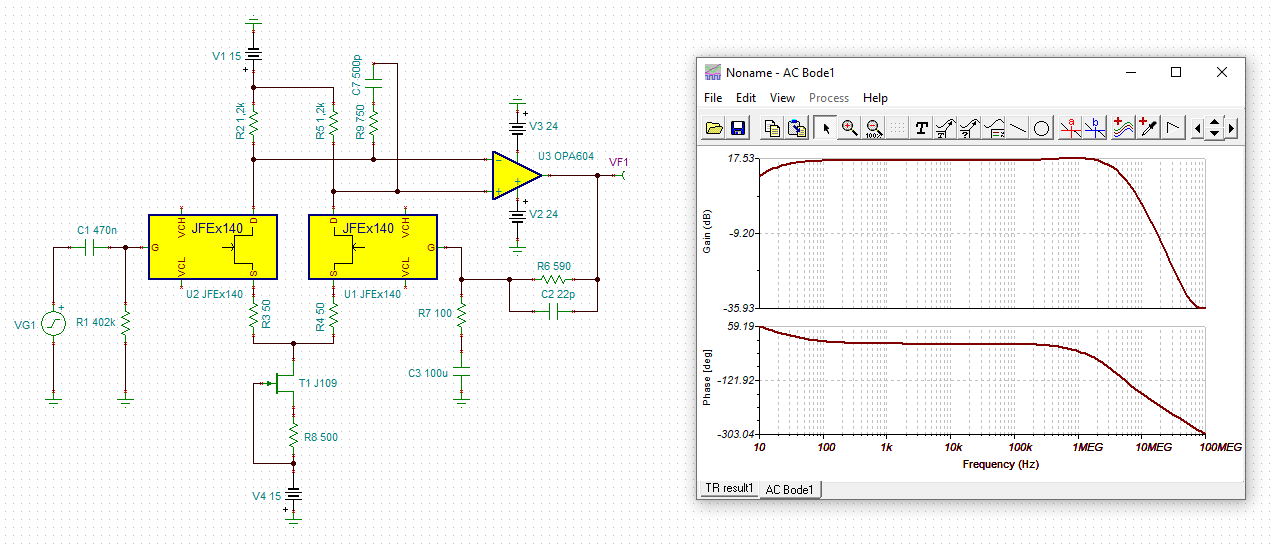

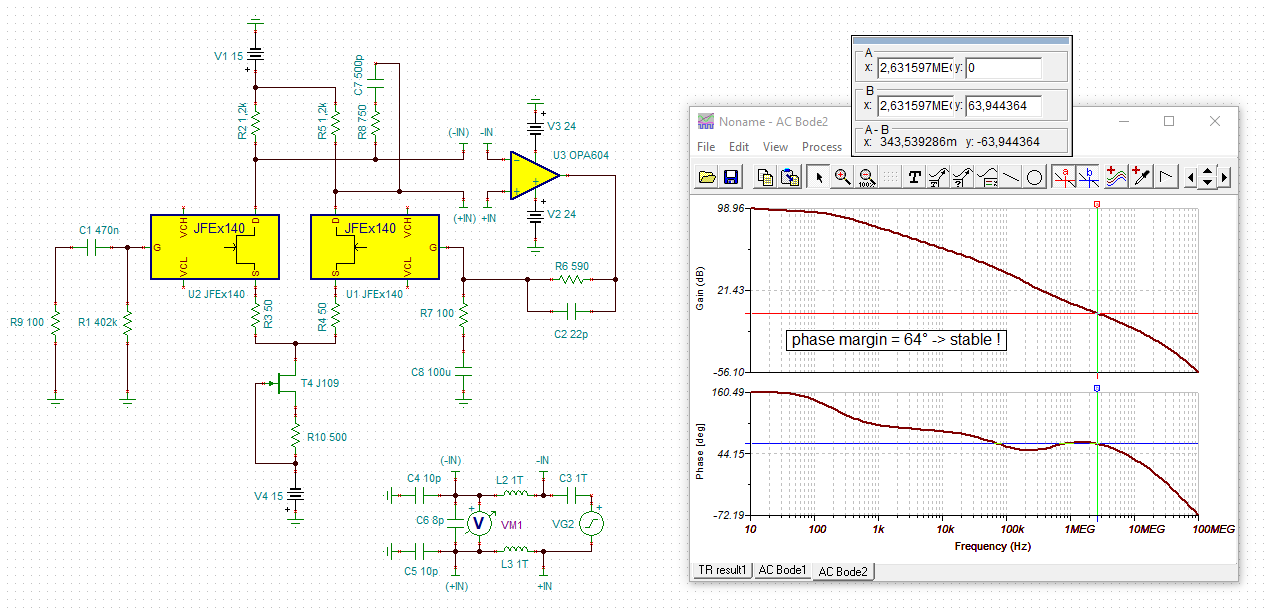

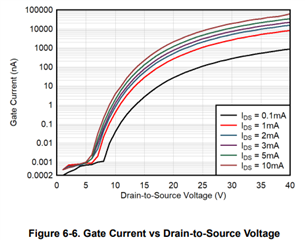

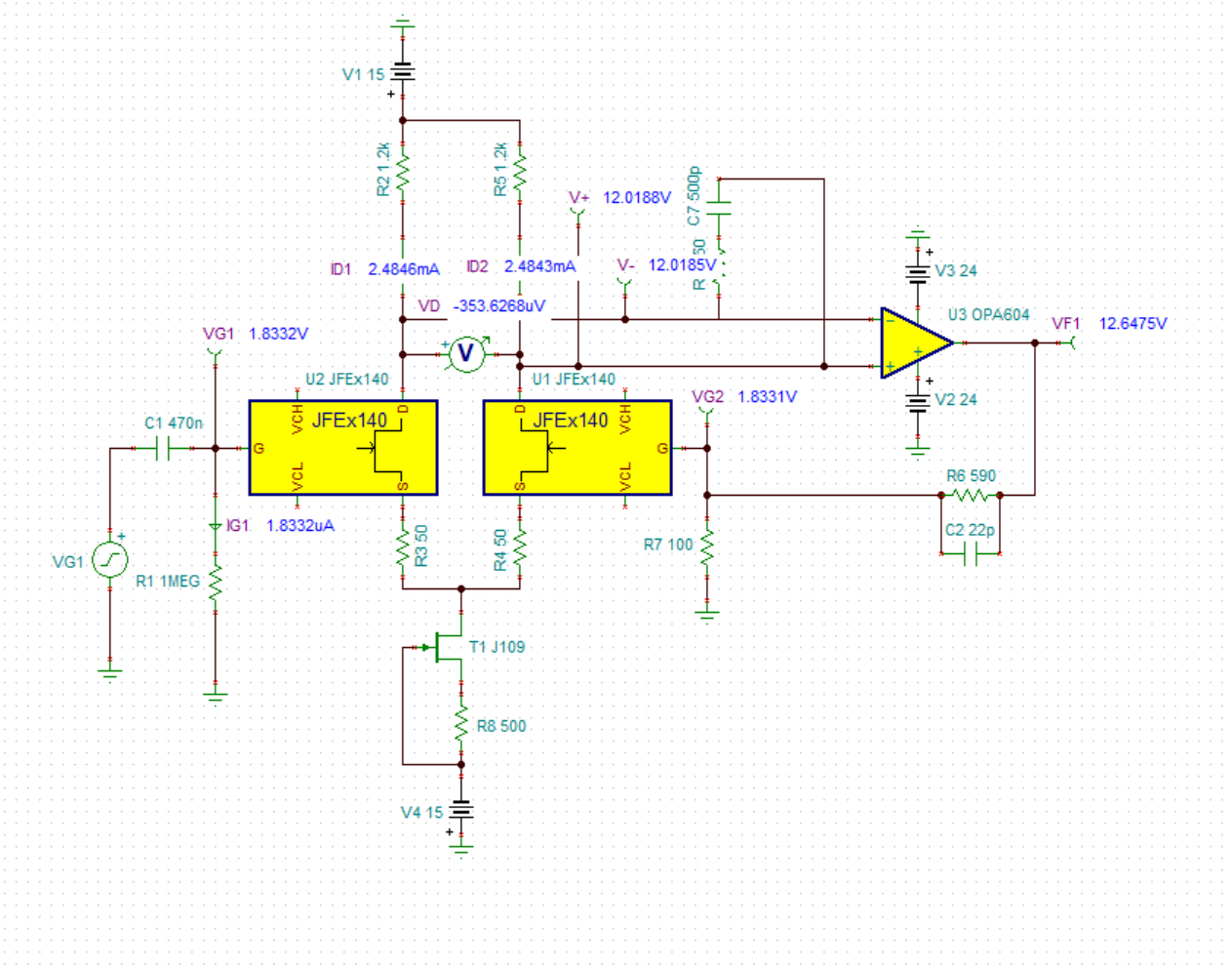

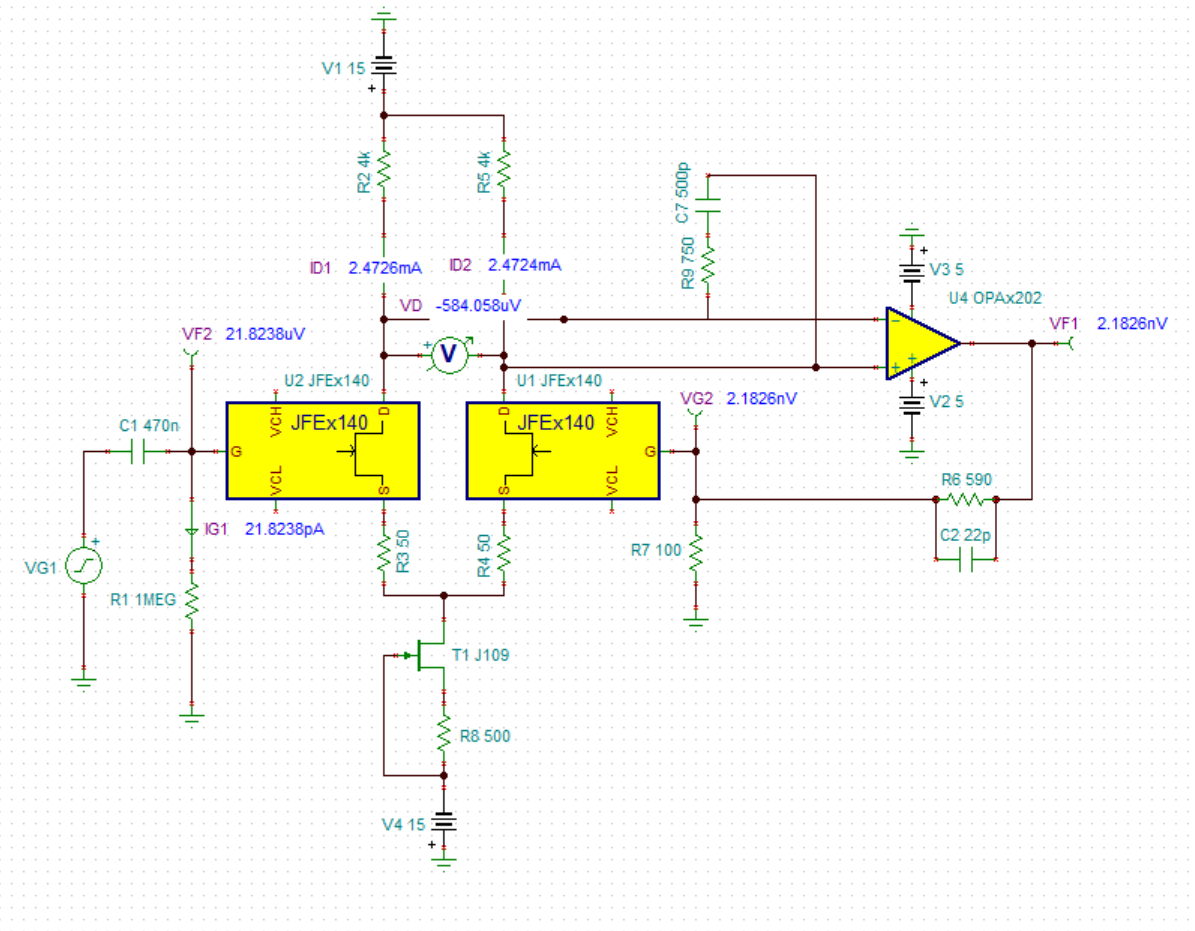

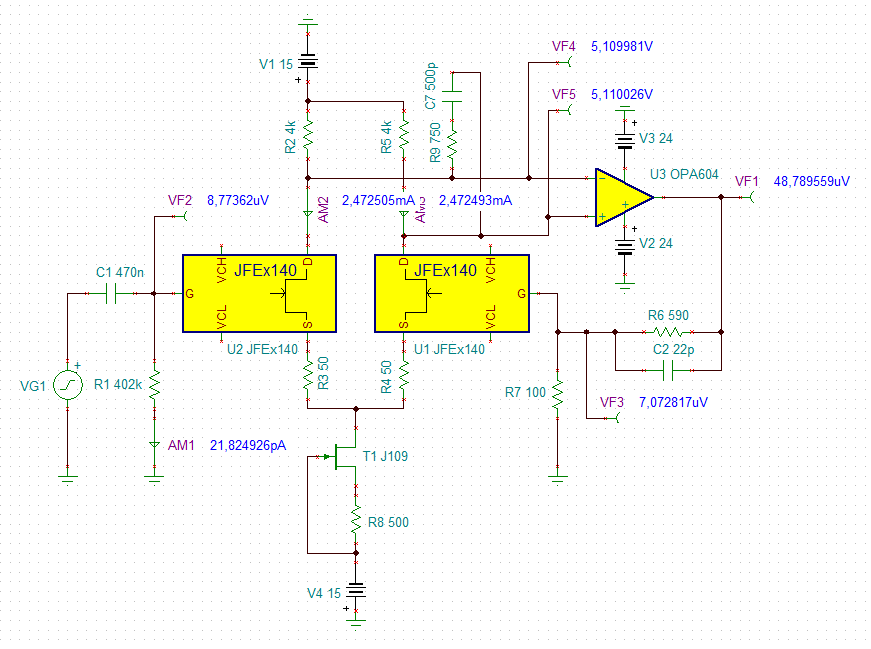

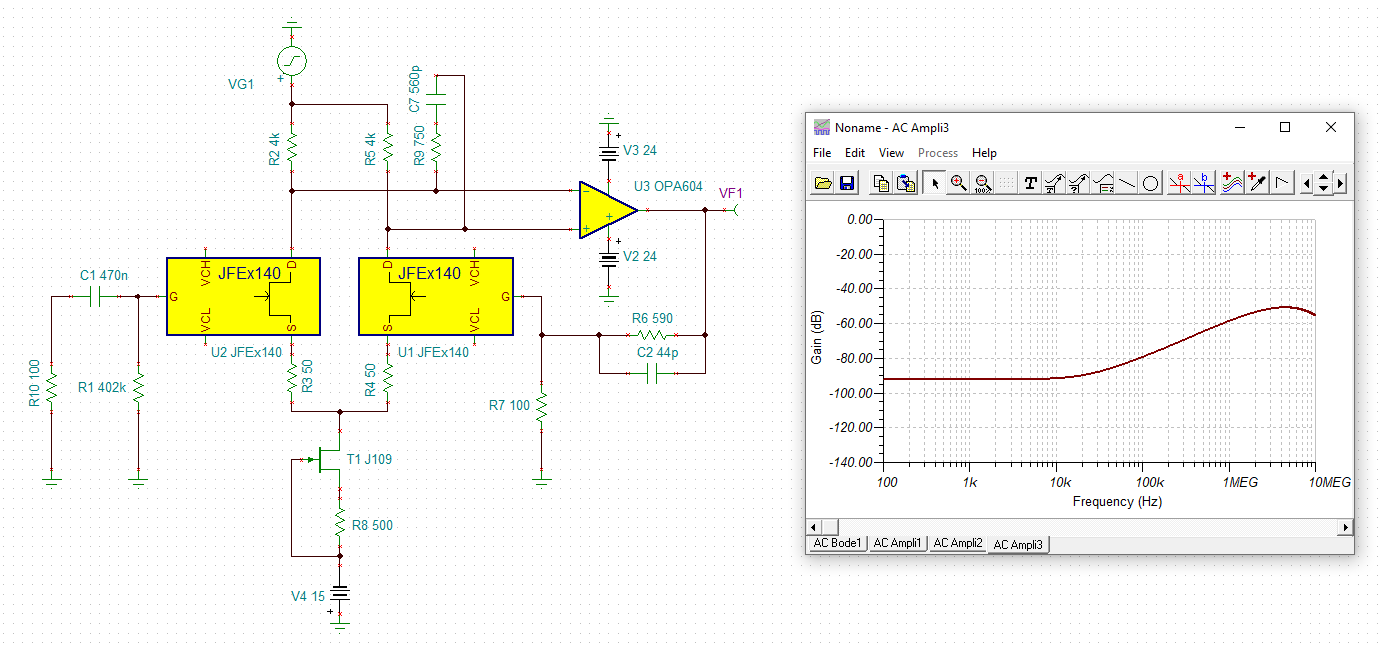

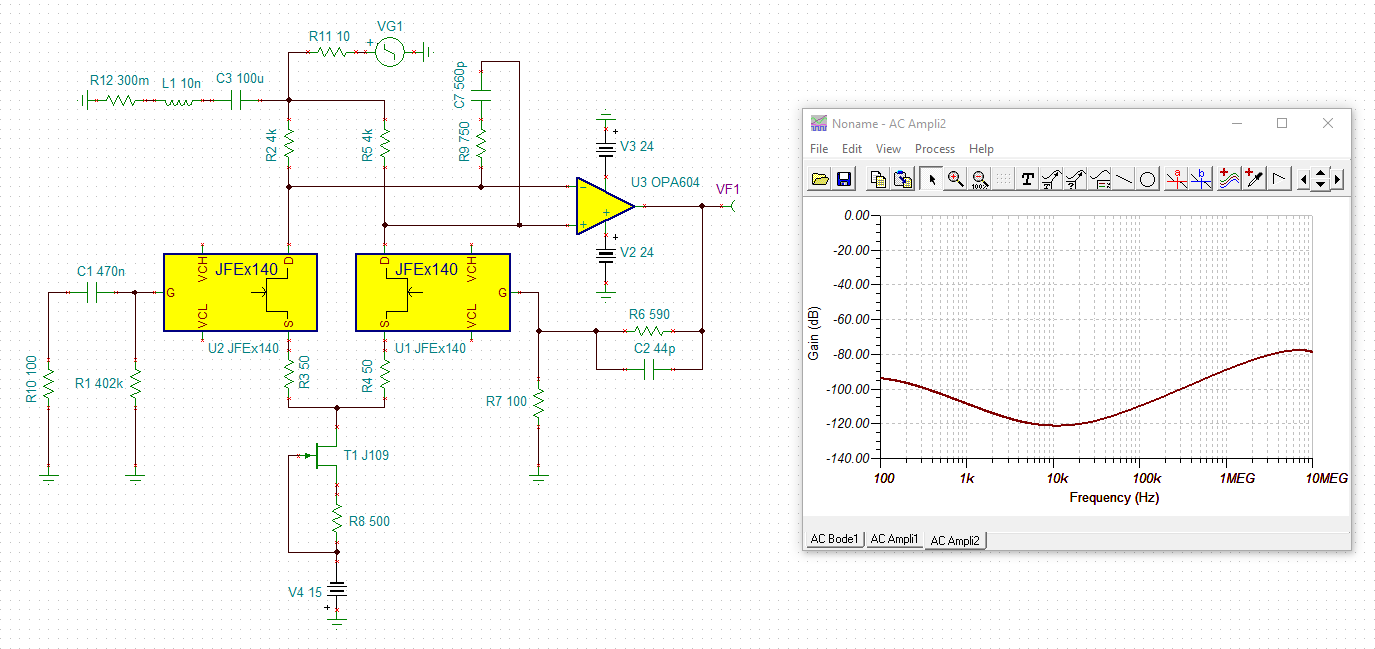

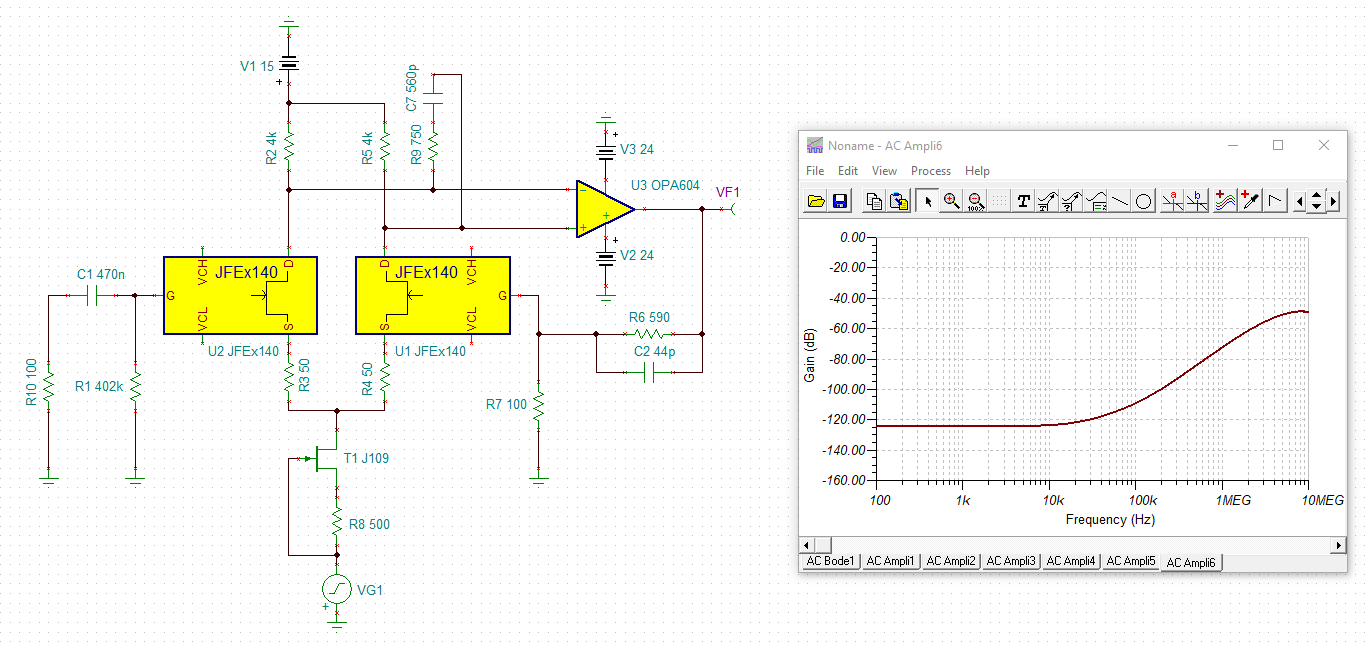

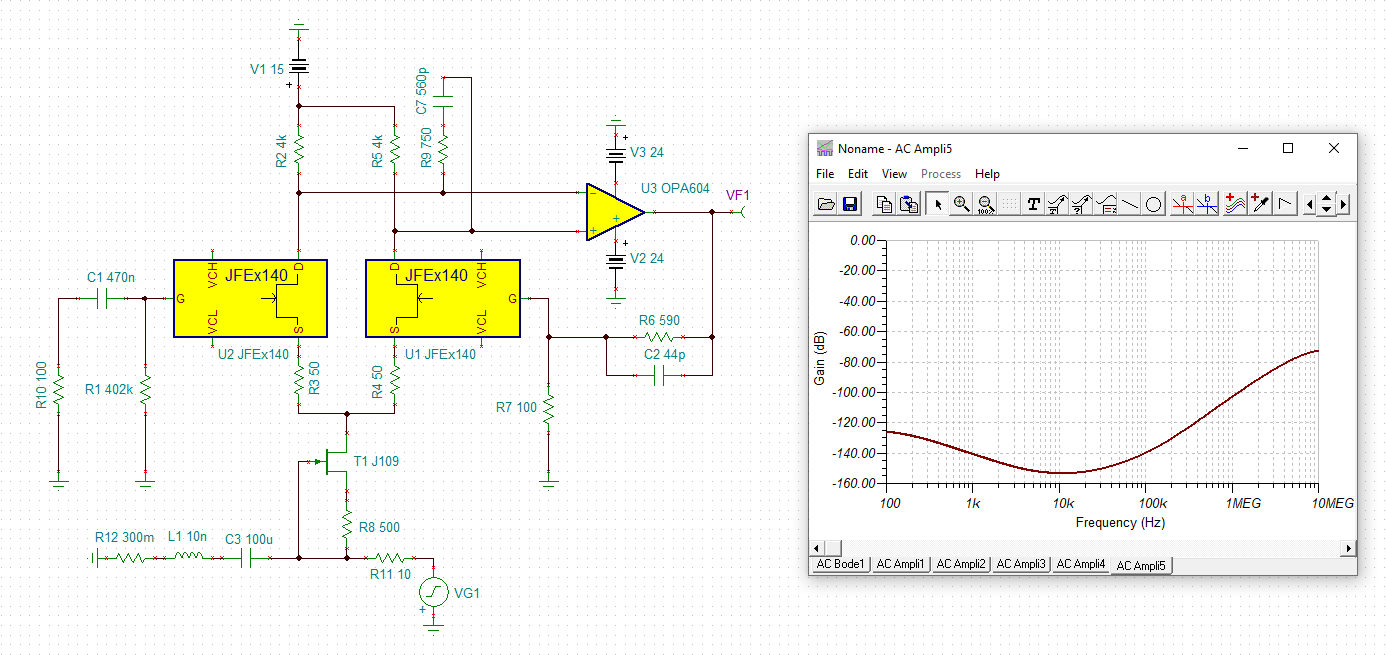

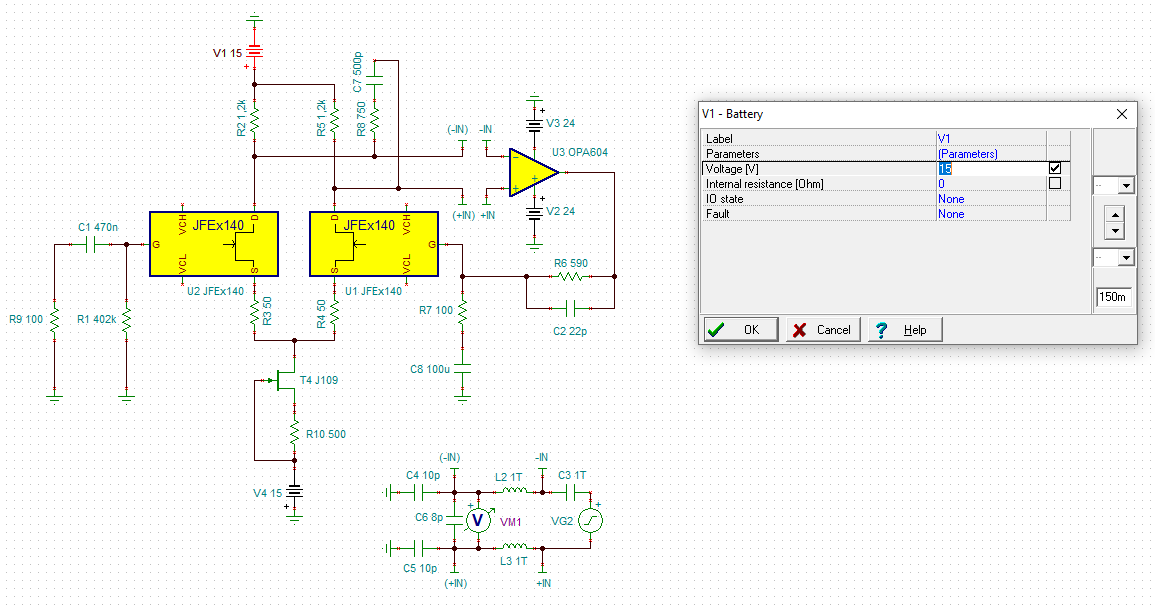

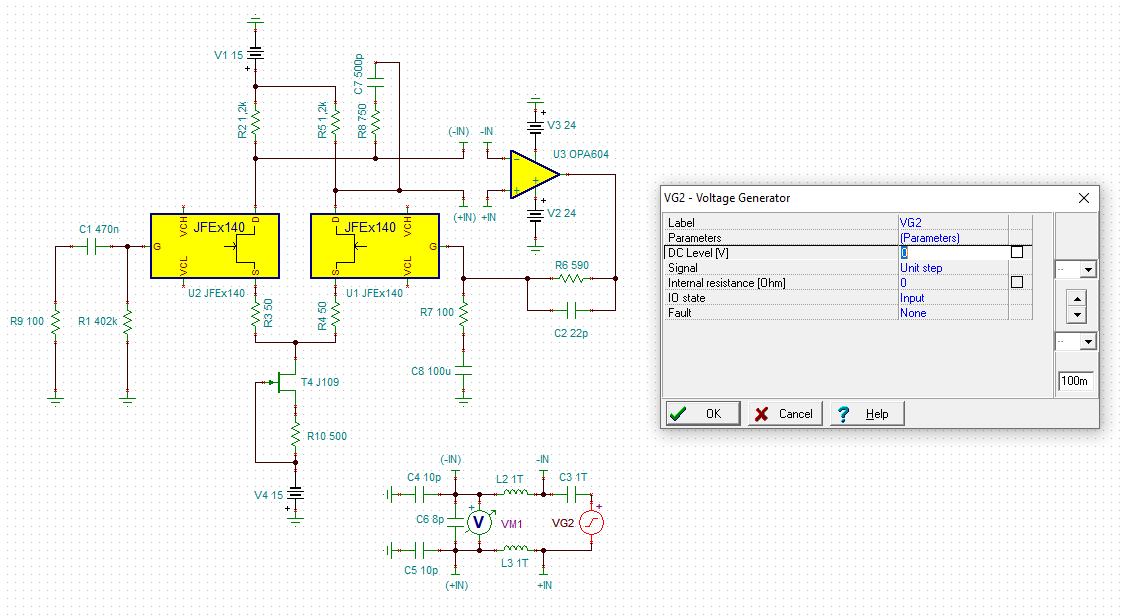

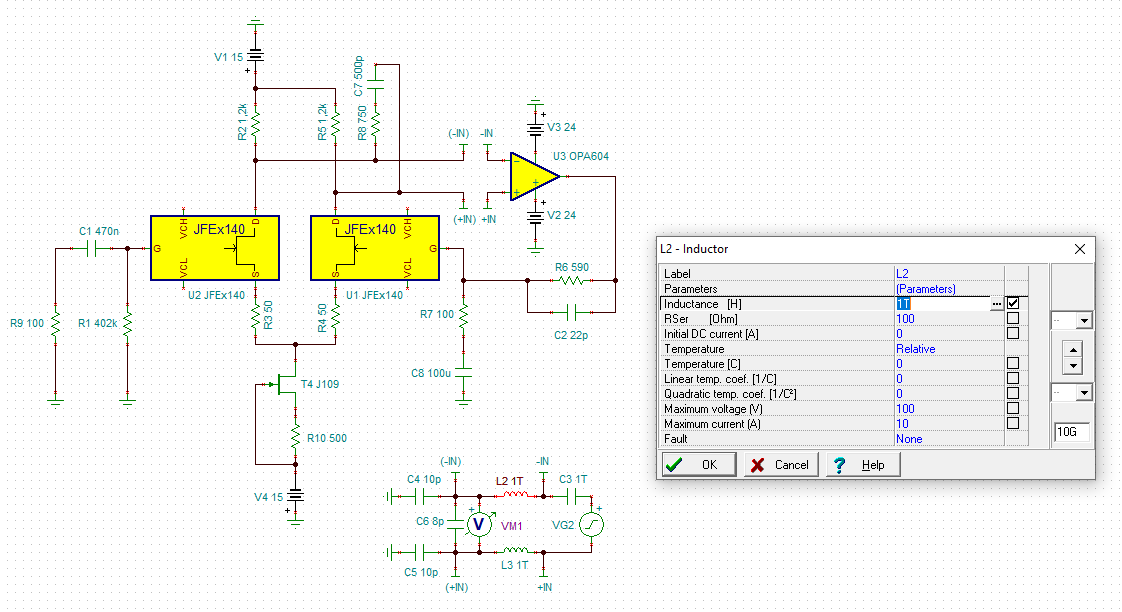

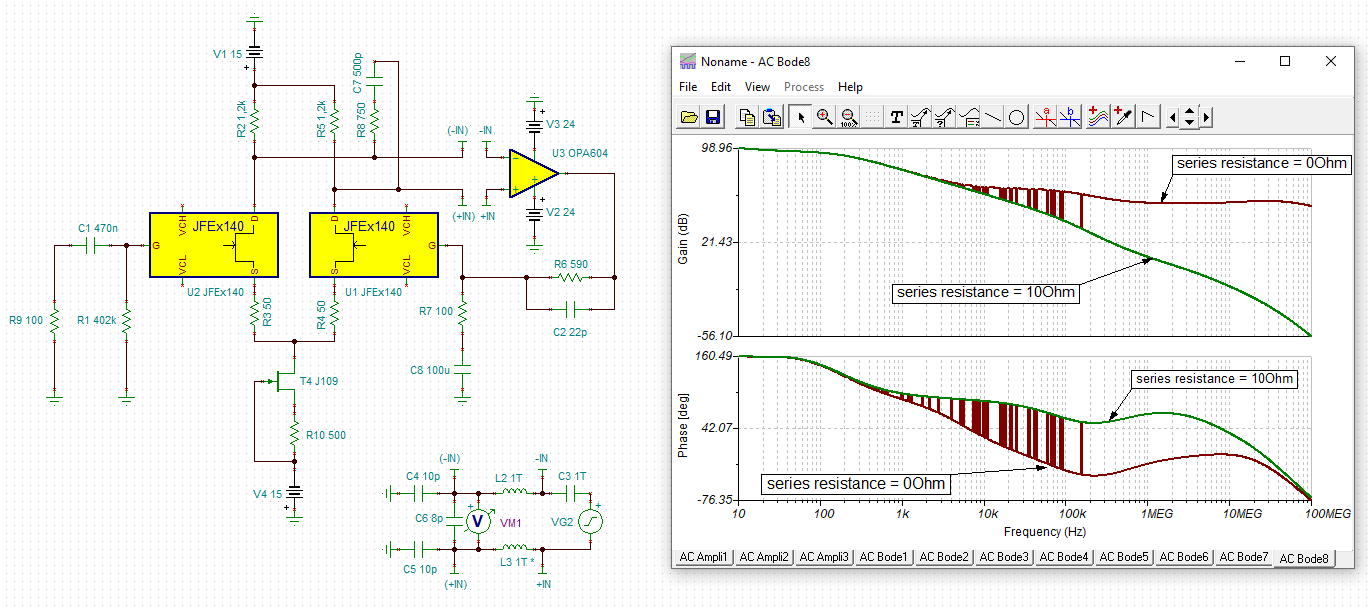

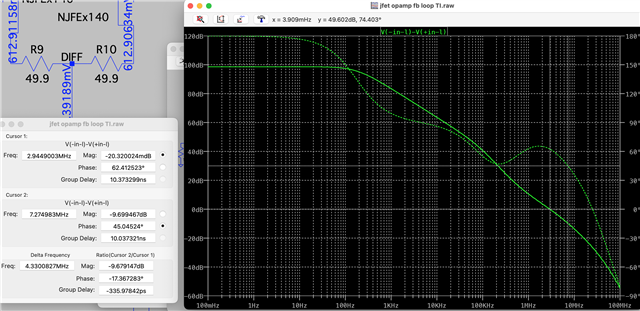

我使用 JFE2140双路 JFET 和 OPA604构建了复合放大器、如图 JFE2140 DS 上的9-6。 两个我已经构建好了、但另两个表现出 直流增益。 随着输入增加、直流输出变为正。 当我测试第一个具有此功能的电路时、我认为必须存在布线错误、我无法找到该错误、直到我构建另一个具有相同问题的电路。 我已经用尽了对这两个问题示例进行故障排除的能力。 LTSpice 未显示任何问题。 (我不相信 PSPICE-TI 支持我的 Mac OS、但如果支持、请告知我。)

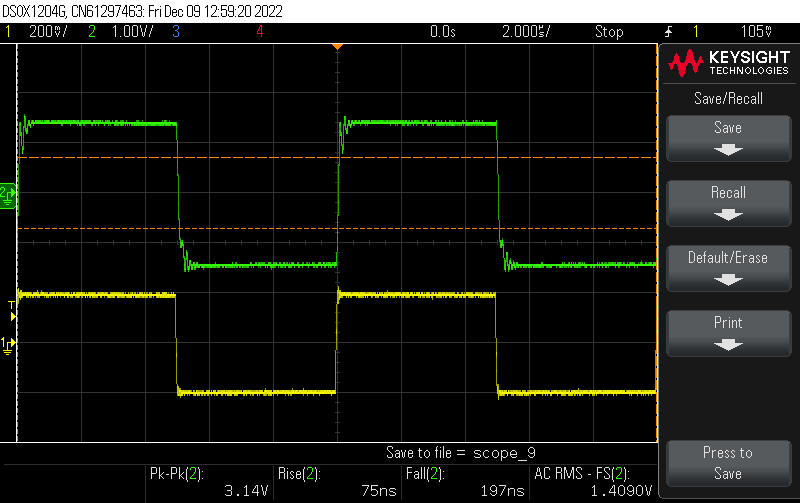

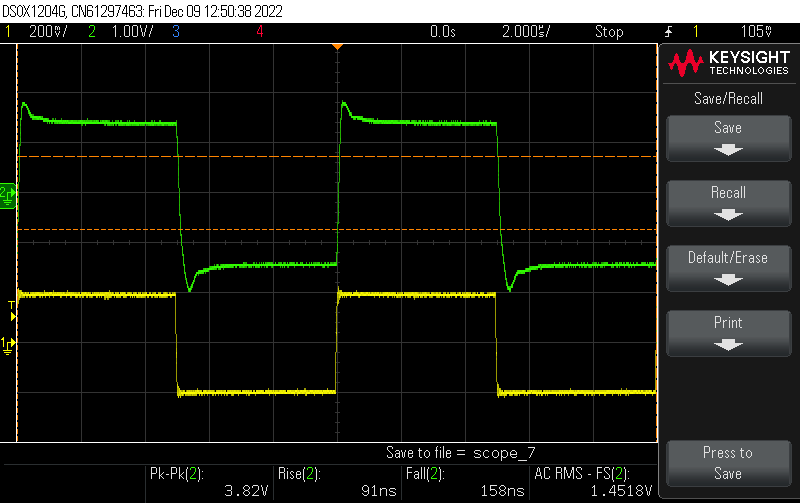

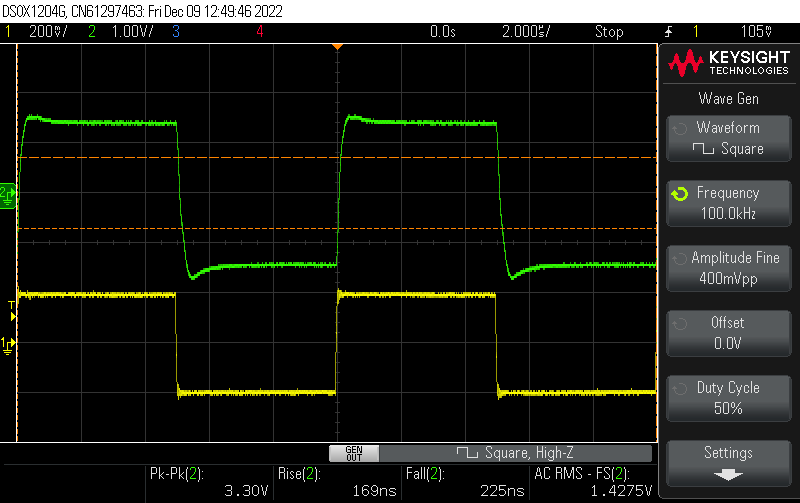

总增益应约为7、并且我有一个输入阻断电容器、因此第一个 JFET 栅极的输入端唯一的直流电流主要是 由电路中的不平衡引起的。 但是、当输入交流信号为1伏 RMS 时、输出端的失调电压超过1伏。 输入信号处的1.75V 峰值会产生5.4V 直流输出。

原理图如下。

我缺少什么? 提前感谢。

e2e.ti.com/.../jfet-opamp-fb.pdf