各位专家:

向 CX 寻求您对此问题的帮助:

我需要有关 INA333差模输入阻抗的技术设计支持。

我尝试在 LTSpice 中对其 Z_D 进行仿真。 我想知道输入偏置电流返回路径如何影响 Z_D 因为当我尝试使用该偏置路径仿真 Z_D 时、我看不到数据表中提到的任何高 Z_D。

是否有 Z_D 过频图? 我只是想了解外部电路如何影响在源极处看到的 Z_D。

您是否了解如何仿真差模阻抗或如何测量差模阻抗?

此致、

阿尔基·A.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

各位专家:

向 CX 寻求您对此问题的帮助:

我需要有关 INA333差模输入阻抗的技术设计支持。

我尝试在 LTSpice 中对其 Z_D 进行仿真。 我想知道输入偏置电流返回路径如何影响 Z_D 因为当我尝试使用该偏置路径仿真 Z_D 时、我看不到数据表中提到的任何高 Z_D。

是否有 Z_D 过频图? 我只是想了解外部电路如何影响在源极处看到的 Z_D。

您是否了解如何仿真差模阻抗或如何测量差模阻抗?

此致、

阿尔基·A.

您好、Archie、

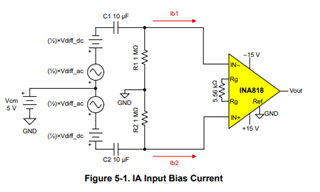

我相信您所指的配置与下图5-1类似、其中 R1和 R2为 INA 的输入偏置电流提供直流接地路径。

对于上述电路、 IN-输入节点的阻抗是与1MΩ Ω 电阻器 R1并联的 INA (INA333为100GΩ Ω)的输入阻抗。 1MΩ 100G >> 1MΩ Ω、100GΩ Ω 与1MΩ Ω 并联约等于 Ω。 这可能是您无法在仿真中"看到"INA 的高输入阻抗的原因、因为您可以看到与输入电路并联的高输入阻抗。

您正尝试仿真什么?

您能否提供电路原理图?

在考虑输入偏置电流返回路径时、本应用手册可能会有所帮助: https://www.ti.com/lit/an/sboa503/sboa503.pdf?ts=1674088678032&ref_url=https%253A%252F%252Fwww.ti.com%252Fproduct%252FINA333

此致、

扎赫

Zach 和 Kai、您好!

感谢您的参与。 客户体验回应:

想象一下、面对该配置、阻抗约为数百千欧至1兆欧姆的电源:

源信号约为 µV μ V 至 mV。 现在我们将使用一个具有偏置电流返回路径的分压器,并且源(信号)不会看到 INA 的高输入阻抗,对吧?

我认为这是非常难过的–因为高输入阻抗的优势会消失。

到目前为止、我是对的吗? 如果是、是否有权变措施?

谢谢你。

此致、

阿尔基·A.

您好、Archie、

我将在这里输入芯片;在使用直流阻断电容器时、始终需要偏置输入。 需要记住的一点是、用于偏置输入的阻抗越高、器件启动时稳定所需的时间常数就越长。 一个100M Ω 电阻器、连同所示的10nF 电容、将创建一个1秒的时间常数、因此加电后可能需要几秒钟的时间来稳定。 如果信号很小、有时人们会使用二极管 代替电阻器、因为它们具有非常低的反向电流、如果信号足够小、则二极管不会正向偏置。

但总的来说、与 Kai 一致、除非您可以去掉直流阻断电容器。没有任何其他实际的选择。

此致、

Mike