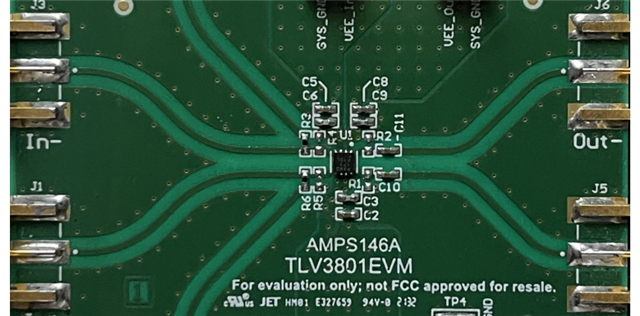

主题中讨论的其他器件: TLV3801、 TLV3811、 TLV3801EVM、TLV3601

对于低于200MHz 的输入、输出为方波、当输入大于200MHz 时为锯齿波。 这是预期吗?

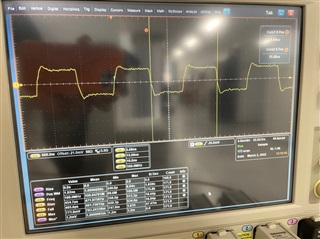

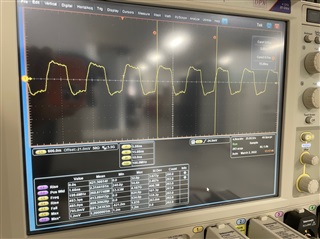

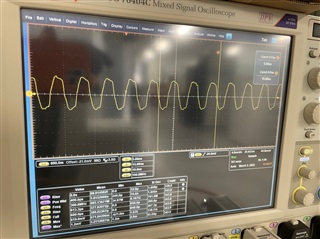

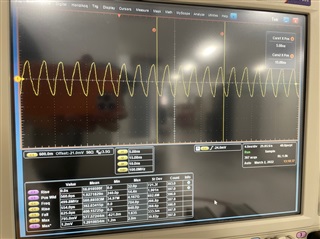

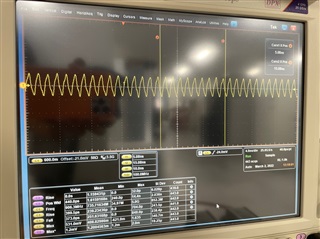

下面是 TLV3604 输出的屏幕截图、其中包含不同的输入频率:

1.100MHz 正弦波输入

2.200MHz 正弦波输入

3. 300 MHz 正弦波输入

4. 500MHz 正弦波输入

5. 900MHz 正弦波输入

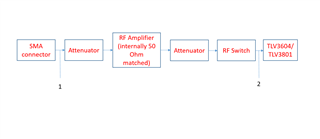

在最终 应用中、来自光电倍增管或离子检测器的 TLV3604输入将是窄至1ns 的脉冲、而比较器的输出将被发送到 FPGA 进行计数。 我的问题是-

1.上述屏幕截图中描述和描述的行为是否符合预期?

2.如果该行为在预料之内,您能否推荐其它速度可达1ns 的比较器器件型号。

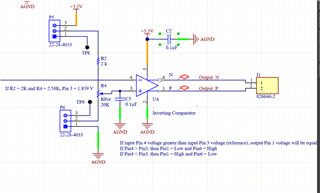

3、如果不希望出现这种行为,原因可能是什么? 我将附上我们正在使用的电路原理图、希望收到有关原理图的反馈。

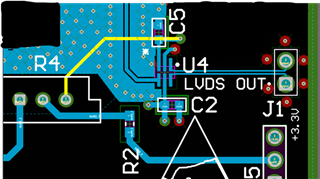

此电路采用4层布局制造完成。 请查看此处所附的布局屏幕截图。 屏幕截图中是–

- 顶层(1)为蓝色、接地(2)为绿色、电源(3)为红色、底部(4)为黄色。

- TLV3604 (U4)引脚4的输入为单端共面50欧姆控制阻抗、两侧都有屏蔽过孔。 顶层的参考接地层是第2层。

- R4电位计的引脚1接地 。

- J1是一个带有接地过孔的双引脚公头 Molex 接头。

- 所有测量均使用具有100欧姆差分探头的示波器完成。

- C2是引脚5的旁路电容器、尽可能靠近 U4放置。 它是0.1 μ F µF±50V 陶瓷电容器 X7R 0603 (公制1608)。

电 µF±C5为0.1 μ F 10% 50V 陶瓷电容器 X7R 0603 (公制1608)。 我曾尝试将其从电路板上移除、LVDS 输出看起来和之前一样、在低于200MHz 的频率下是方波、在高于200MHz 的频率下是锯齿波。

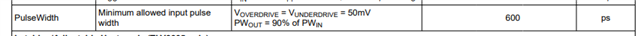

对于原型测试、输入为正弦波、但对于最终应用、输入将是脉宽为1ns 的短脉冲。

您能否提供有关如何实现尽可能接近数据表规格的更快上升和下降时间的反馈。 如果我能提供更多详细信息、请告诉我。 谢谢你