主题中讨论的其他器件: OPA855、OPA858

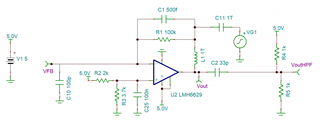

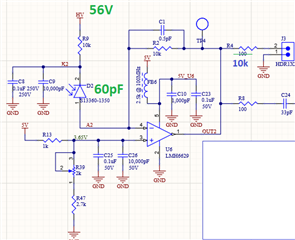

我正在尝试使用 LMH6629 通过 Hamamtsu S13360 MPPC 进行单光子检测。

来自 MPPC 的电流脉冲既小又快。 我相信它们处于10µA μ s 范围内、并且持续时间为10ns、具体取决于输入的阻抗。

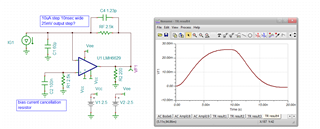

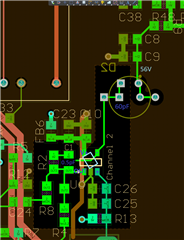

我遇到了700MHz 范围内放大器振荡的问题。 增大反馈电容器(C1)会使振荡变得更糟。 我移除了器件下方和 MPPC 阳极迹线(A2)周围的接地 。 这很有用、但我必须在 LMH6629顶部放置一个1000pF 去耦电容器来减少振铃。

它目前运行良好、但我仍具有以下目标:

- 提高稳定性–是否可以注入信号来测量相位裕度? 我想知道、如果 MPPC 的电容稍高、它就不会振荡。

- 较高频增益

在我的应用中、我只关心对光子数量进行计数。 我不需要知道它们到达的时间。