主题中讨论的其他器件:LMP7704、 OPA837

您好!

我正在寻找 SNOAA75A (航天级100krad 125kHz 光电二极管 TIA 电路)中提供的 TINA 模型文件、

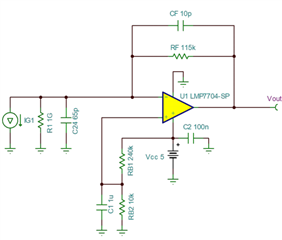

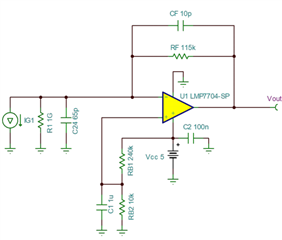

下面显示了 pdf 代码片段。

感谢您的帮助!

但以理

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我正在寻找 SNOAA75A (航天级100krad 125kHz 光电二极管 TIA 电路)中提供的 TINA 模型文件、

下面显示了 pdf 代码片段。

感谢您的帮助!

但以理

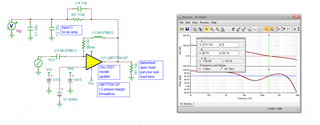

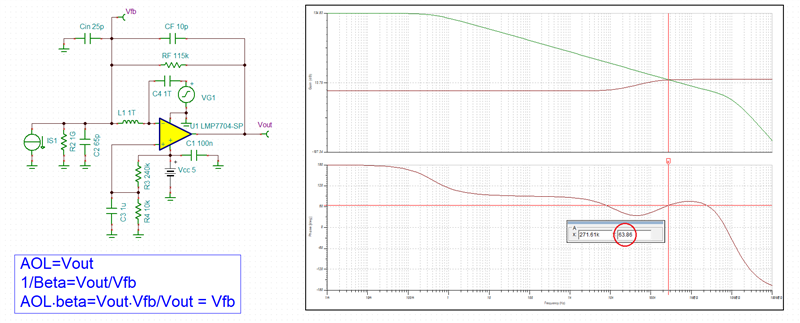

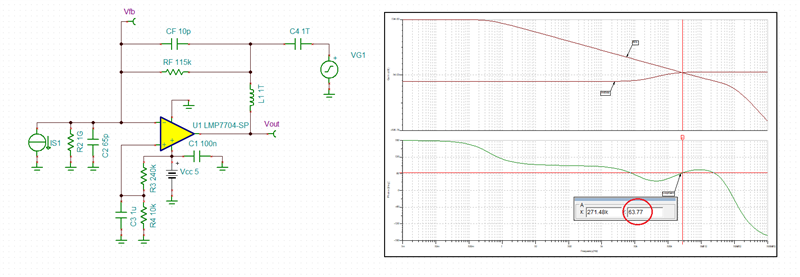

好的、从2021年的模型更新来看、这里有一个 LG 仿真设置更好一点、包括了 LMP7704的寄生输入 C、该输入 C 相当高、64度非常好、但可能会因寄生 C 负载而迅速降低。

这是 TINA V9中的这个文件

e2e.ti.com/.../LMP7704SP-Zt-LG-test.TSC

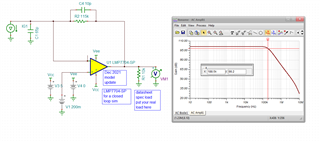

然后您的闭环仿真、非常好的平坦188kHz 设计、

这个仿真文件、

e2e.ti.com/.../LMP7704SP-Zt-closed-loop.TSC

还有一些模型测试、GBP 看起来不错、Zol 非常奇怪、模型中似乎有高输入 C、

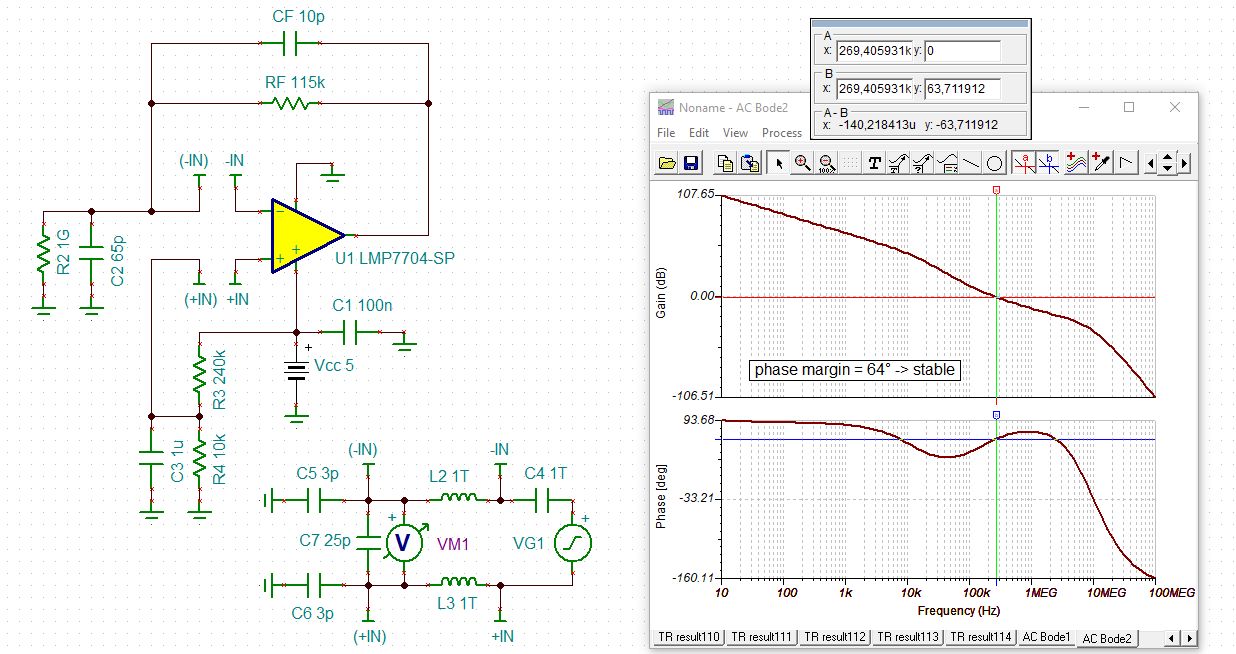

是的、通过使用两种不同的方法、我可以确认电路看起来相当稳定、具有64度的相位裕度-见下文。

你敢打赌丹尼尔,

嗯、Marek、我需要找出我在 zol sim 上做了什么错、

我在本文中用 OPA837以及该输出注入技术展示了一个更严重的错误、此外还介绍了传统文献中存在的一些其他注意事项

好的、我在反相输入端向接地添加了99.97mF 电容、结果得到了很大的澄清、我认为这与数值抖动升高 F 的情况相关。我正在使用2021年12月模型更新、这确实看起来非常合理。

Daniel、您好!

我得到这个用于相位稳定性分析的结果:

e2e.ti.com/.../daniel_5F00_lmp7704.TSC

凯

是的、Kai、我认为这是一个更彻底的方法、我有时也会使用它。我认为您已经对 Cdiff 至 CCM 的拆分进行了猜测、如果数据表中的3pF CCM 和25pFis 是我找不到的。 对于 V+接地的简单 ZT 级、我们通常只使用单个 CCM + Cdiff 进行设计。

遗憾的是、很多数据表中都缺少这种级别的准确详细信息- 我们在这里找到了许多器件、这些器件的数字都是错误的、在大多数情况下、Ccm 在 CMOS 输入级中>> Cdiff。 我将使用20pF CCM 和5pF Cdiff 尝试它。 现在看到64度,仍然很好,基本上这种设计是非常稳定的,所有这些以后的讨论是甲科学陷阱。