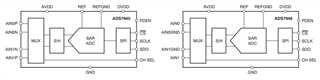

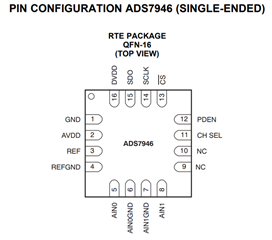

主题中讨论的其他器件: OPA320、OPA357 、ADS7945、ADS7946

您好、我们可能对此感到担忧、

以下是对这种情况的描述:

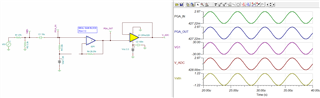

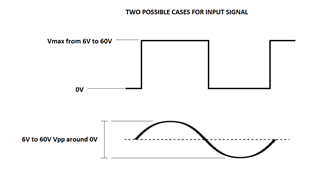

1.输入信号:系统需要能够捕获两种类型的信号(来自 BLDC 或 PMSM 电机相位)、对于每种类型、信号可改变其幅度、如下所示:

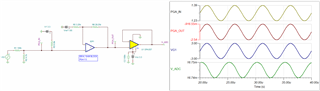

正弦波:偏移为零时、最大 Vpp = 60V;偏移为零时、最小 Vpp = 6V;

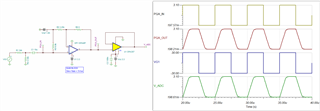

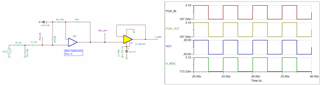

*最大频率的 PWM 200kHz:最大振幅=60V、最小振幅=6V、所有这些最小电平的理想值为0V。

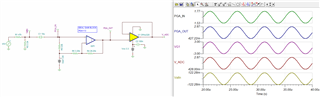

这两个信号的表示如下:

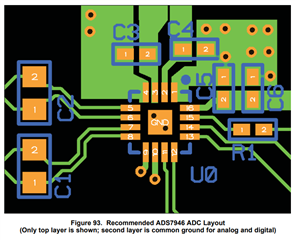

2. ADC:12位,采样率为0.5uS (最大需要)

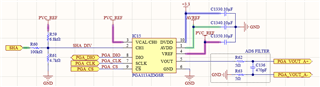

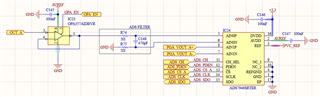

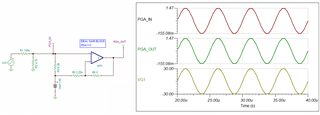

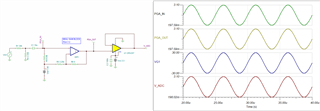

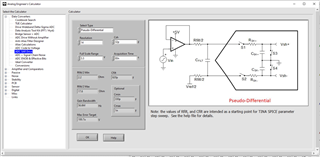

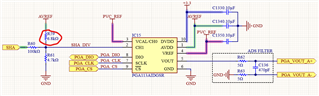

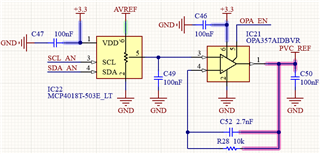

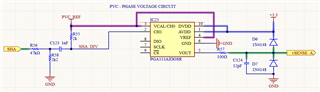

为了能够处理该信号、建议使用以下电路:

知道了所有这些、我们有一些问题:

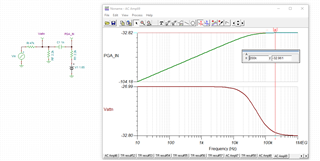

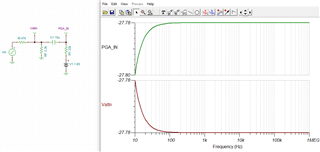

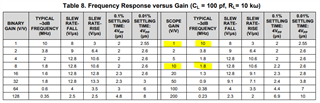

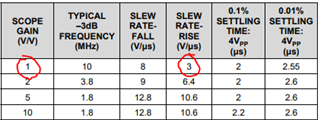

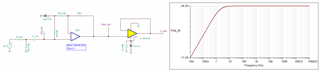

1.此系统的 PGA 增益1到10的实际闭环带宽是多少?

2.此实际闭环带宽是否 与12位 ADC @ 0.5uS 采样率兼容?